# Prabhat Mishra University of Florida

## Introduction

The goal of this project is to develop an efficient dynamic reconfiguration framework to enable adaptive computation, communication and storage in heterogeneous multicore SoCs under energy, performance, reliability, thermal and real-time constraints.

Reconfiguration Primitives

- Dynamic voltage and frequency scaling

- Dynamic task mapping to CPU/GPU cores

- > Dynamic NoC reconfiguration

- > Dynamic cache reconfiguration

### Objectives / Constraints

> Power, performance, energy, reliability, temperature and real-time constraints

## Motivation

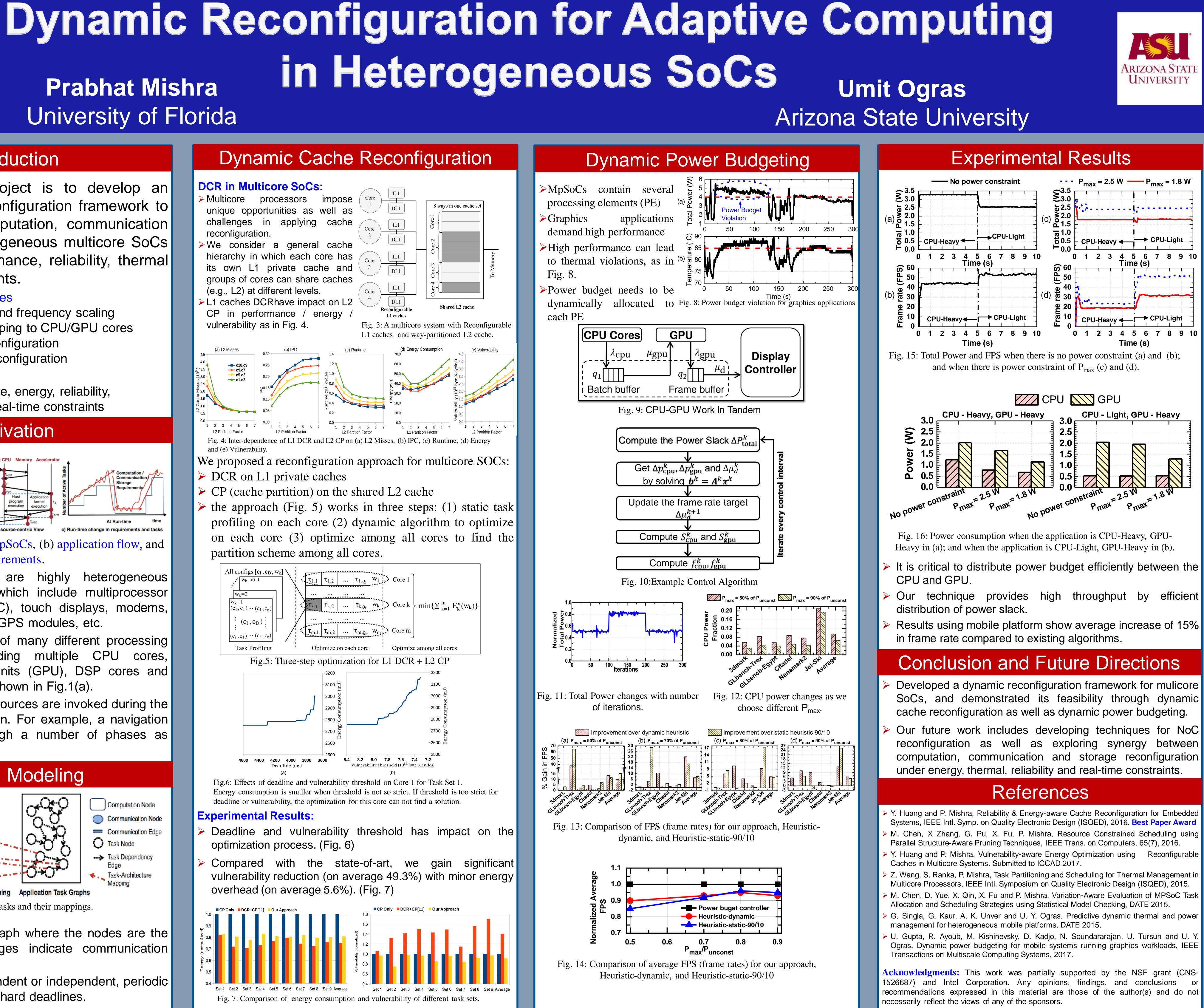

Fig.1: (a) Heterogeneous MpSoCs, (b) application flow, and (c) run-time change in requirements.

- Embedded systems are highly heterogeneous computing platforms, which include multiprocessor system-on-chip (MpSoC), touch displays, modems, flash memory, camera, GPS modules, etc.

- MpSoC itself consists of many different processing elements (PE) including multiple CPU cores, graphical processing units (GPU), DSP cores and video accelerators, as shown in Fig.1(a).

- Only a subset of the resources are invoked during the lifetime of an application. For example, a navigation application goes through a number of phases as illustrated in Fig. 1(b).

## System Modeling

Computation Node Communication Node

Communication Edge Task Node

--- Task Dependency

Task-Architecture

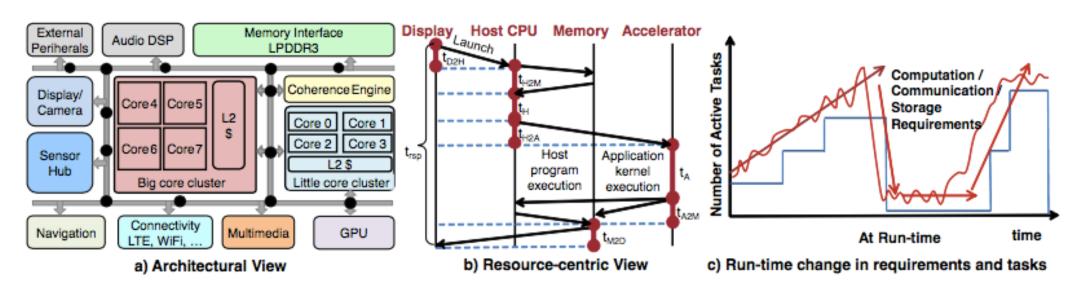

Fig.2: Modeling of architecture, tasks and their mappings.

- The task model is a graph where the nodes are the set of tasks and edges indicate communication between tasks.

- The tasks can be dependent or independent, periodic or aperiodic with soft or hard deadlines.