# **Digital Circuits**

ECGR2181 Chapter 3 Notes

Reading: Chapter 3

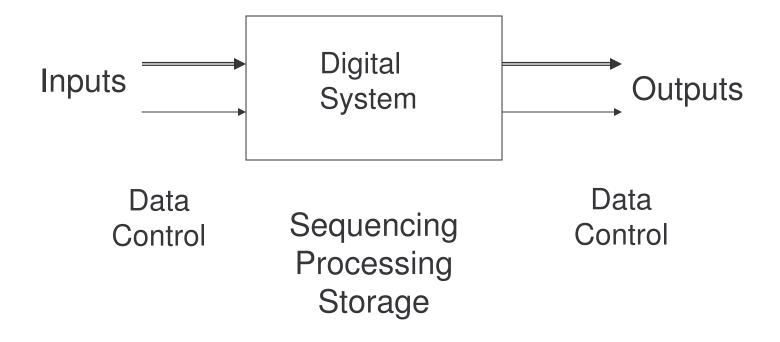

# What is a digital system?

It is a organized collection of digital elements which is designed to perform specified operations on a set of digital inputs and to generate a set of digital responses.

A digital system can be as simple as a block of combinational logic or as complex as a microprocessor.

# **Characteristics of Digital Systems**

#### What are the characteristics of a digital system?

- Coordinate and sequence its internal operations.

- Data processing and storage.

- Cooperate in transferring data to & from itself.

- Sequences operations of external entities.

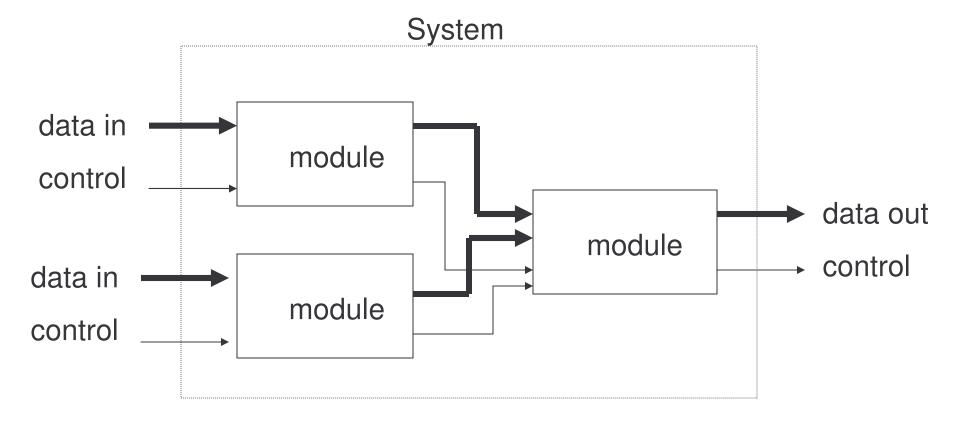

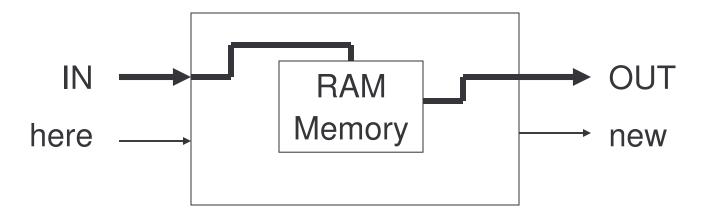

# Overview of a digital system

# **Input & Output Signals**

#### Data:

Multi-bit: "values"

•Single-bit: decision-making / information

Control: {generally single-bit signals}

- Sequencing operations of system

- Coordinating operations with external units

**Nomenclature:** (Terms to know.)

**Word**: A group of binary bits. Typically represents some element of data. The number of bits in a word is <u>indeterminate</u> unless specified. [Example: "24-bit word"]

Byte: An 8-bit word.

Nibble: A 4-bit word.

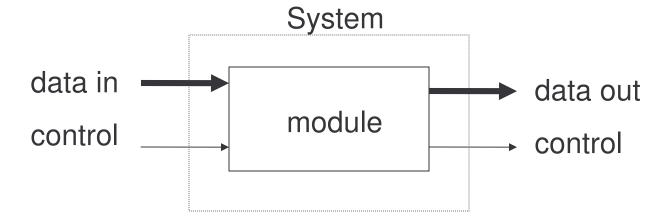

Structure of digital systems: "system" vs. "module"

- A digital system can be created as a monolithic structure.

- Complex systems often need to be partitioned into some number of subsystems -- "modules"

- For small systems which can be conveniently designed monolithically the terms "system" and "module" may be used interchangeably.

### Single module system:

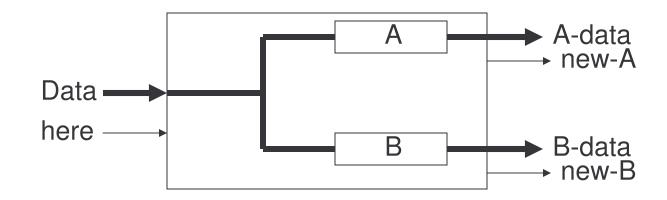

### Multiple module system:

### **Examples of digital systems**

- Data Selector: Route input data to one of two outputs.

- <u>Data Converter:</u> Inputs a 32-bit data word and outputs it as 4 bytes.

- Message Generator: Outputs a fixed message when a "start" command is received

- Communications Buffer: Receives and stores a "block"

of data. When the block is

complete, it resends the

stored data.

- Microprocessor: "Does everything!"

# A first look at the design process

- 1. Understand the functional specification.

- 2. Create a block diagram from the external viewpoint.

- 3. Fill in the major internal components.

- 4. Determine the sequence of operations which must occur within the module

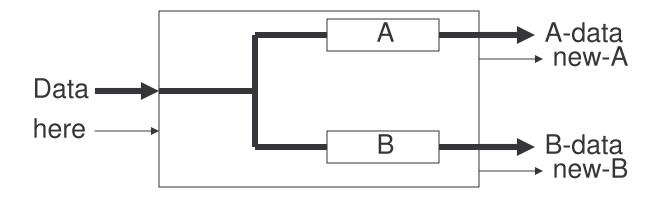

#### **Data Selector**

Route input data to one of two outputs.

Specification: When a new data word arrives at the input, the module inspects the state of the most significant bit and routes the data to output A if the bit is true and to B if the bit is false. The last value sent to either output is retained until replaced.

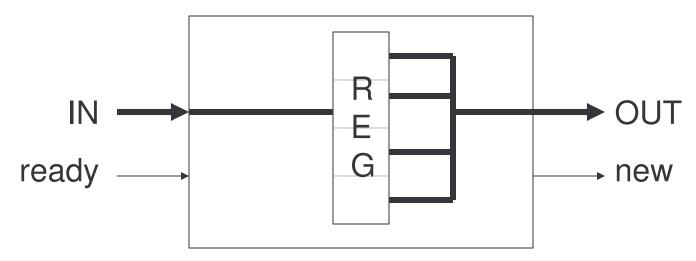

#### **Data Converter**

Inputs 32-bit data word and outputs it as 4 bytes.

Specification: When a new data word arrives at the input, the module accepts it and then outputs the word as 4 bytes.

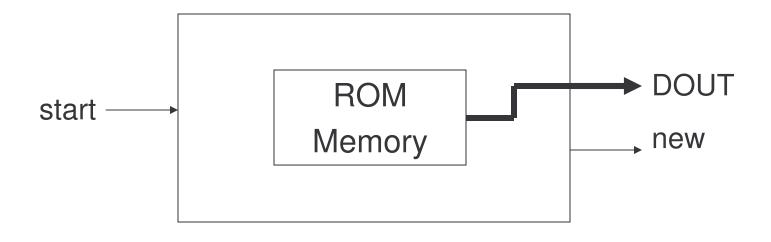

### **Message Generator**

Outputs a fixed message when a "start" command is received.

<u>Specification</u>: When a "start" command is received, the module retrieves the bytes of a message stored in an internal ROM and outputs them sequentially.

#### **Communications Buffer**

Receives and stores a "block" of data. When the block is complete, it resends the data.

Specification: The module receives a series of data bytes and stores them in an internal memory. Intake of data stops when a byte of all 1's is received. Then it resends the message with pairs of bytes packed in 16-bit words.

### **Digital Logic**

Binary system -- 0 & 1, LOW & HIGH, negated and asserted. Basic building blocks -- AND, OR, NOT

(b)

$$\frac{X}{Y}$$

$X OR Y$   $X + Y$

| Χ | Υ | X OR Y |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

(c)

$$X \longrightarrow NOT X$$

| X | NOT X |

|---|-------|

| 0 | 1     |

| 1 | 0     |

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

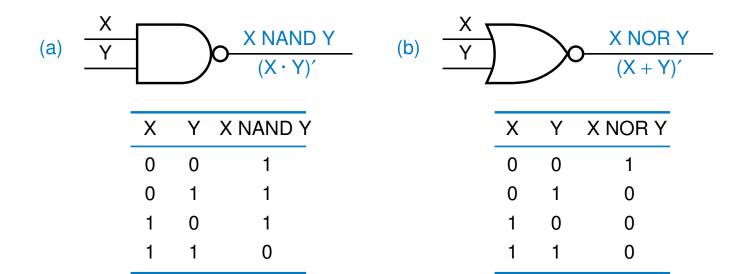

### **NAND** and **NOR**

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

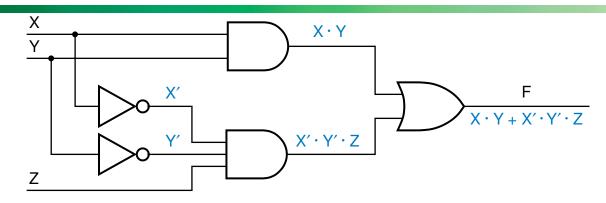

### **Truth Tables**

| X | Y | Z | XY | X' | Y' | X'+Y'+Z | F |

|---|---|---|----|----|----|---------|---|

|   |   |   |    |    |    |         |   |

|   |   |   |    |    |    |         |   |

|   |   |   |    |    |    |         |   |

|   |   |   |    |    |    |         |   |

# **More Practice**

| X Y Z | F |

|-------|---|

|       |   |

|       |   |

|       |   |

|       |   |

# Many representations of digital logic

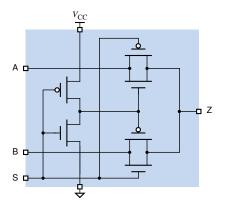

Transistor-level circuit diagrams

### **Truth tables**

Α

В

Z

S

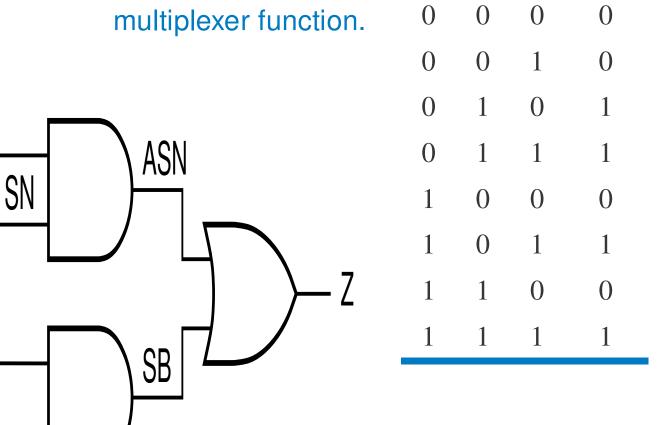

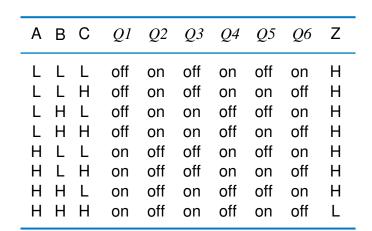

### Table 1-1

Truth table for the er function.

| Logic diagrams | multiplexe |

|----------------|------------|

| Α ———          | ASN        |

### Logic levels

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

Switching threshold varies with voltage, temp, process, etc.

need "noise margin"

Operating closer to the tolerances requires an increase in attention to "analog" behavior.

Logic voltage levels decreasing with process

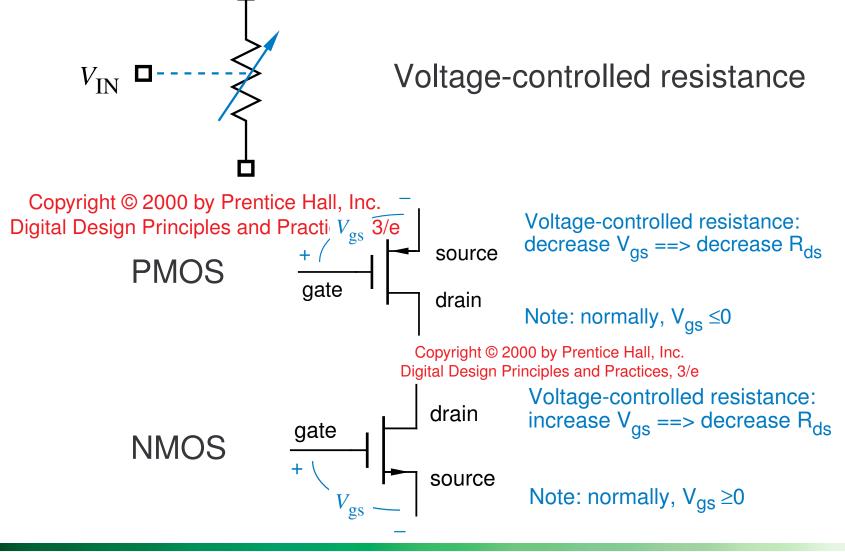

#### **MOS Transistors**

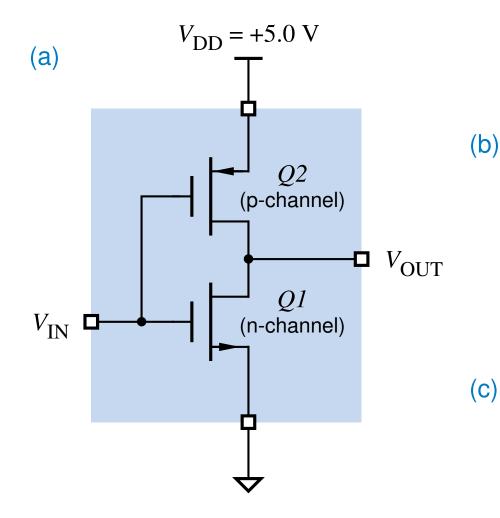

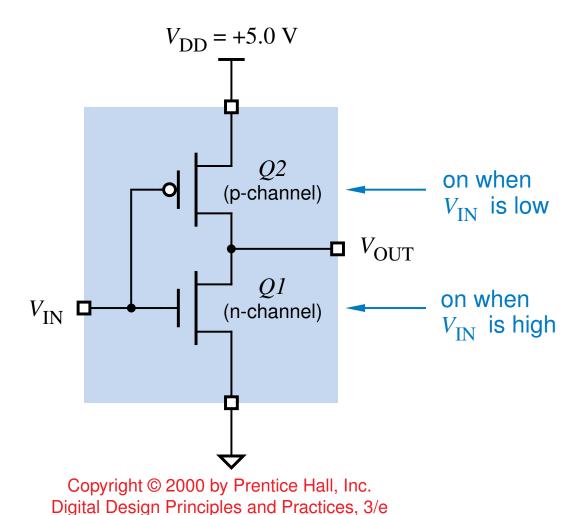

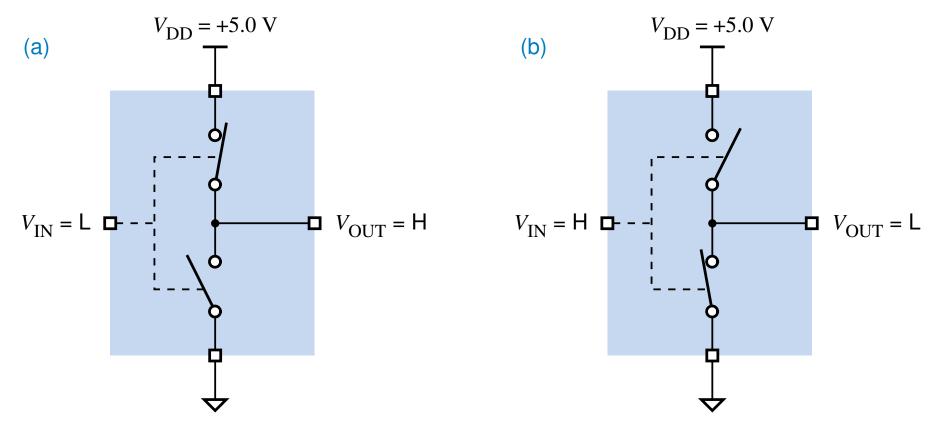

### **CMOS Inverter**

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

| $V_{ m IN}$ | Q1  | <i>Q</i> 2 | $V_{ m OUT}$ |

|-------------|-----|------------|--------------|

| 0.0 (L)     | off | on         | 5.0 (H)      |

| 5.0 (H)     | on  | off        | 0.0 (L)      |

IN OUT

### **Alternate transistor symbols**

### Switch model

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

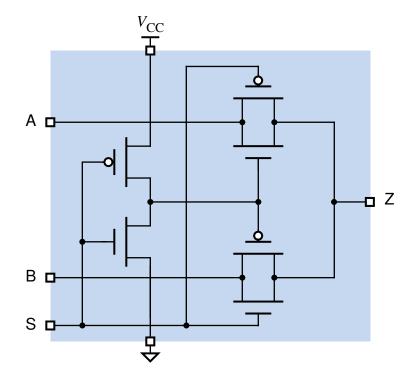

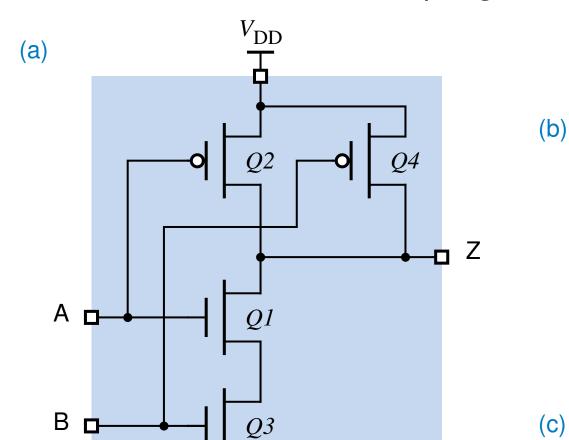

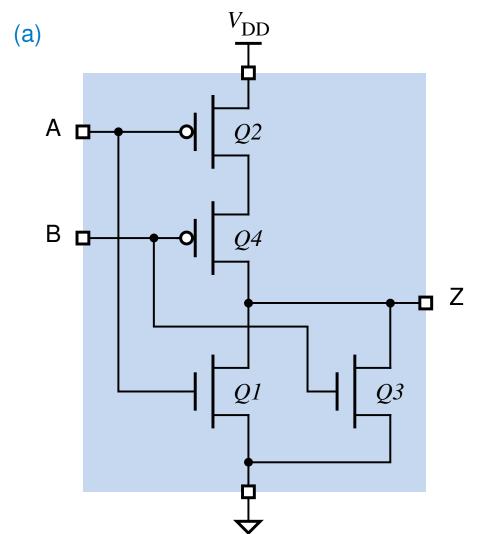

### **CMOS NAND Gates**

### Use 2*n* transistors for *n*-input gate

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

| A B                      | Q1        | Q2        | <i>Q3</i> | <i>Q4</i> | Z      |

|--------------------------|-----------|-----------|-----------|-----------|--------|

| L L<br>L H<br>H L<br>H H | off<br>on | on<br>off | on<br>off | off<br>on | H<br>H |

Z В

(b)

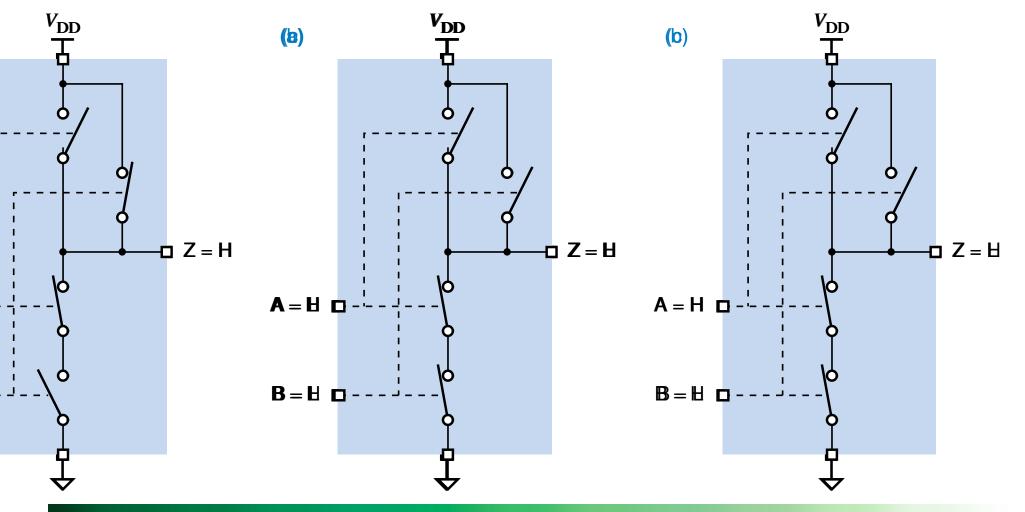

#### CMOS NAND -- switch model

Α

В

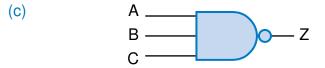

### CMOS NAND -- more inputs (3)

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

(b)

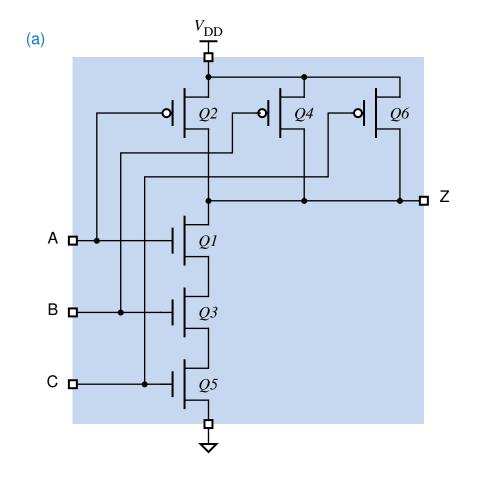

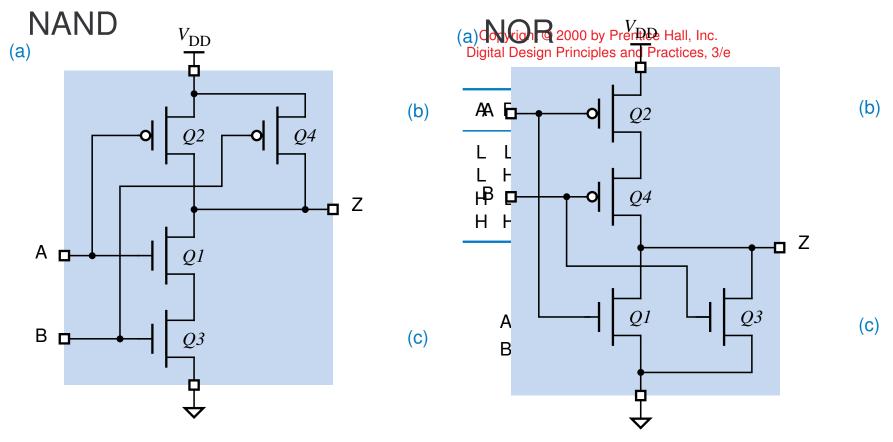

### **CMOS NOR Gates**

Like NAND -- 2n transistors for n-input gate

| (b) | Α      | В      | Q1               | Q2        | Q3        | Q4        | Z      |

|-----|--------|--------|------------------|-----------|-----------|-----------|--------|

| ,   | L<br>H | H<br>L | off<br>off<br>on | on<br>off | on<br>off | off<br>on | L<br>L |

|     | Н      | Н      | on               | off       | on        | off       | L      |

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

(c)

#### NAND vs. NOR

PMOS transistors have higher "on" resistance than NMOS transistors.

Result: NAND gates are preferred in CMOS.

Copyriq Digital De