ECGR2181 Extra Notes

Reading: Chapter 4.7

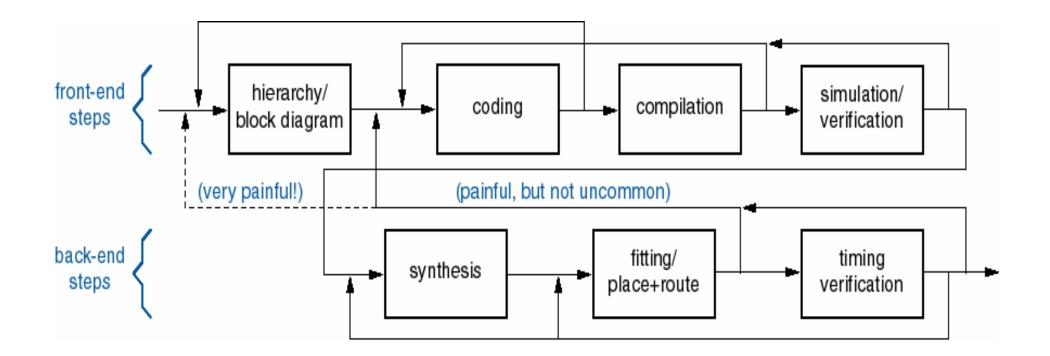

For ASICs, verification and fitting phases are usually much longer (as a fraction of overall project time) than what you've experienced in class.

# VHDL

Developed in the mid-1980s under DoD sponsorship

- Mandated for federally-sponsored VLSI designs

- Used for design description, simulation, and synthesis

- Synthesis became practical in the early 90s and use of VHDL (and Verilog) has taken off since then

Only a subset of the language can be synthesized

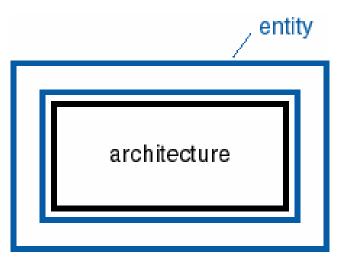

## VHDL entity and architecture concept

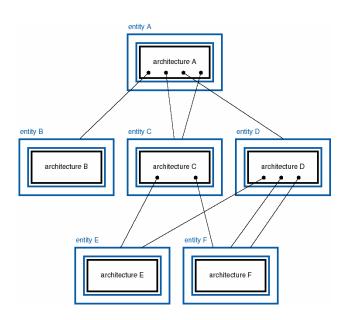

System is a collection of modules.

- Architecture: detailed description of the internal structure or behavior of a module.

- Entity: a "wrapper" for the architecture that exposes only its external interfaces, hiding the internal details.

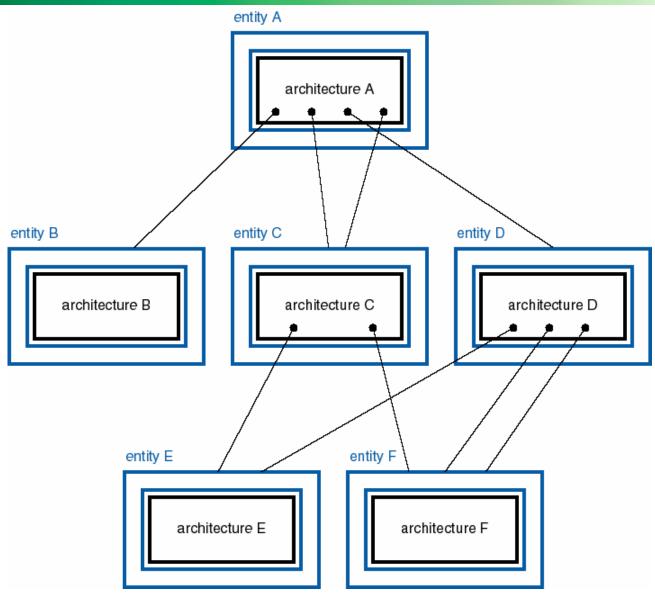

## **VHDL Hierarchy**

### **VHDL program file structure**

\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_

| text file (e.g., mydesign.vhd) |                                                                                                                  |  |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| entity declaration             | entity Inhibit is<br>port (X,Y: in BIT;                                                                          |  |  |  |  |  |

|                                | Z: out BIT);<br>end Inhibit;                                                                                     |  |  |  |  |  |

| architecture definition        | architecture Inhibit_arch of Inhibit is<br>begin<br>Z <- '1' when X-'1' and Y-'0' else '0';<br>end Inhibit_arch; |  |  |  |  |  |

Entity and architecture definitions for different modules can be in different files.

Compiler maintains "work" library and keeps track of definitions using entity and architecture names.

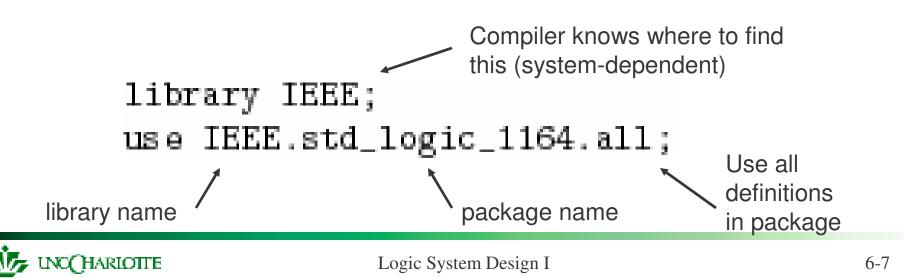

# VHDL -- designed by committee

Tries to be all things to all people.

- Result -- very general, but also very complex.

- Standard logic values and elements are not built-in.

- Standard logic defined by a "package", IEEE 1164 STD\_LOGIC.

- Must be explicitly "used" by program.

## Standard logic values -- not just 0,1

Need additional values for simulation, three-state logic, pullups, etc.

- Defined in IEEE 1164 STD\_LOGIC package.

```

type STD_ULOGIC is ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

subtype STD_LOGIC is resolved STD_ULOGIC;

```

### Logic functions defined by table lookup

| <b></b> 1 | υI                 | х         | 0    | 1        | Ζ        | W        | L    | Н         | _        |      | I |    |

|-----------|--------------------|-----------|------|----------|----------|----------|------|-----------|----------|------|---|----|

| -         | יטי).              | <br>יווי  | 101  | <br>יווי | <br>ידדי | <br>יווי | 101  | <br>יוווי | <br>יווי | ·    | 1 | тт |

|           | , יטי)             |           |      | •        | -        |          | -    | -         |          |      |   |    |

|           | ('0',              |           |      |          | -        | _        | -    | -         |          | -    |   |    |

|           | ( יטי,             | 'X',      | '0', | '1',     | 'X',     | 'X',     | 101, | '1',      | ' X '    | ), · |   | 1  |

|           | ( יטי )<br>( יטי ) | •         |      |          | •        |          | •    | •         |          |      |   | Z  |

|           | (יטי),<br>(יטי     | -         | -    | -        | -        | -        | -    | -         |          |      | _ |    |

|           | ('0',              | -         | -    | -        | -        | -        | -    | -         |          |      | _ |    |

|           | , יטי )<br>( יטי , |           |      |          |          |          |      |           |          |      |   |    |

|           | 、 o ,              | <i></i> , | Υ,   | а,       | · · ·    | · · ·    | ·· 2 | · · · ·   | 45       | /    | I |    |

FUNCTION "and" ( L : std\_ulogic; R : std\_ulogic ) RETURN UX01 IS BEGIN

```

RETURN (and_table(L, R));

```

END "and";

# VHDL strong typing

Every signal, variable, function parameter, and function result has a "type".

A few built-in types, plus user defined types.

In assignment statements, comparisons, and function calls, types must match.

Commonly used IEEE-1164 types:

- STD\_LOGIC (one bit)

- STD\_LOGIC\_VECTOR(*range*) (multibit vector)

- INTEGER (built-in integer type)

Pain in the neck: Must explicitly convert between INTEGER and STD\_LOGIC\_VECTOR.

```

library IEEE;

architecture parity9p of parity9 is

begin

use IEEE.std_logic_1164.all;

process (I)

variable p : STD LOGIC;

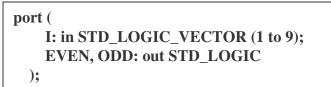

entity parity9 is

variable j : INTEGER;

port (

begin

I: in STD_LOGIC_VECTOR

p := l(1);

(1 to 9);

for j in 2 to 9 loop

if I(j) = '1' then p := not p; end if;

EVEN, ODD: out

end loop;

STD LOGIC

ODD <= p;

);

EVEN <= not p;

end parity9;

end process;

```

end parity9p;

# VHDL programming styles

Structural

- Define explicit components and the connections between them.

- Textual equivalent of drawing a schematic

Dataflow

- Assign expressions to signals

- Includes "when" and "select" (case) statements

Behavioral

- Write an algorithm that describes the circuit's output

- May not be synthesizable or may lead to a very large circuit

- Primarily used for simulation

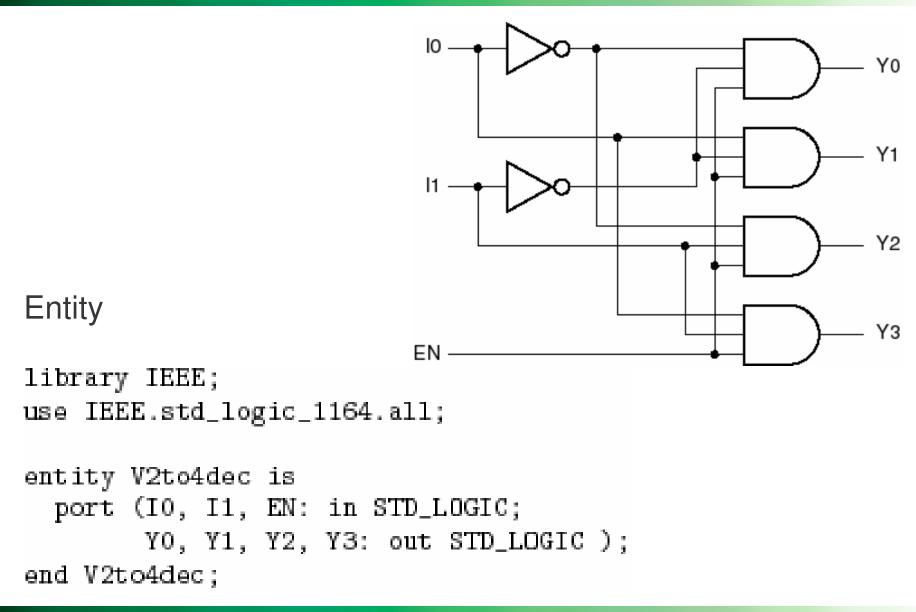

#### Example: 2-to-4 decoder

#### Example: 2-to-4 decoder

#### **Architecture** architecture V2to4dec\_s of V2to4dec is signal NOTIO, NOTI1: STD\_LOGIC; component inv port (I: in STD\_LOGIC; O: out STD\_LOGIC ); end component; component and3 port (I0, I1, I2: in STD\_LOGIC; 0: out STD\_LOGIC ); end component; begin U1: inv port map (IO,NOTIO); U2: inv port map (I1,NOTI1); U3: and3 port map (NOTIO,NOTI1,EN,Y0); NOT IO U4: and3 port map ( IO,NOTI1,EN,Y1); Y0 U5: and3 port map (NOTIO, I1,EN,Y2); U1 U6: and3 port map ( I0, I1,EN,Y3); U3 end V2to4dec\_s; Y1 NOT11 11 U4 U2 positional built-in library Y2 correspondence components U5 with entity definition Y3 EN -U6

#### Dataflow-style program for 3-to-8 decoder

```

library IEEE;

use IEEE.std_logic_1164.all;

entity V74x138 is

port (G1, G2A_L, G2B_L: in STD_LOGIC; -- enable inputs

A: in STD_LOGIC_VECTOR (2 downto 0); -- select inputs

Y_L: out STD_LOGIC_VECTOR (0 to 7) ); -- decoded outputs

end V74x138;

```

## **Dataflow-style program for 3-to-8 decoder**

```

architecture V74x138 b of V74x138 is

signal G2A, G2B: STD_LOGIC;

-- active-high version of inputs

signal Y: STD_LOGIC_VECTOR (0 to 7); -- active-high version of outputs

signal Y_s: STD_LOGIC_VECTOR (0 to 7); -- internal signal

begin

G2A <- not G2A_L; -- convert inputs

G2B <- not G2B_L; -- convert inputs

Y_L <- Y; -- convert outputs

with A select Y s <-

"10000000" when "000",

"01000000" when "001",

"00100000" when "010",

"00010000" when "011",

"00001000" when "100",

"00000100" when "101".

"00000010" when "110",

"00000001" when "111",

"00000000" when others;

Y \leq not Y_s when (G1 and G2A and G2B)-'1' else "00000000";

end V74x138_b;

```

Note: All assignment statements operate concurrently (combinational circuit ).

## Behavioral program style

Normally uses VHDL "processes"

- Each VHDL process executes in parallel with other VHDL processes and concurrent statements

- "Concurrent" statements include assignment and select statements in dataflow-style programs

- Concurrency is needed to model the behavior of parallel, interconnected hardware elements

- But "sequential" statements can be used within a process

#### VHDL process

process (signal-name, signal-name, ..., signal-name)

type declarations

variable declarations

function definitions

procedure definitions

begin

sequential-statement

...

sequential-statement

end process;

A sequence of "sequential

statements".

Activated when any signal in the

"sensitivity list" changes.

Primarily a simulation concept, but can be synthesized

#### **Behavioral version of 74x138**

Except for different syntax, approach is not all that different from the dataflow version

```

architecture V3to8dec_b of V3to8dec is

signal Y_s: STD_LOGIC_VECTOR (0 to 7);

begin

process(A, G1, G2, G3, Y_s)

begin

case A is

when "000" -> Y s <- "10000000":

when "001" -> Y_s <- "01000000";

when "010" -> Y_s <- "00100000";

when "011" -> Y s <- "00010000":

when "100" -> Y s <- "00001000":

when "101" -> Y_s <- "00000100";

when "110" -> Y s <- "00000010":

when "111" -> Y s <- "00000001":

when others -> Y_s <- "00000000";

end case;

if (G1 and G2 and G3)-'1' then Y \leq Y_s;

else Y <- "000000000":

end if;

end process;

end V3to8dec_b;

```

```

architecture V3to8dec_c of V3to8dec is

begin

process (G1, G2, G3, A)

variable i: INTEGER range 0 to 7;

begin

Y <- "000000000";

if (G1 and G2 and G3) - '1' then

for i in 0 to 7 loop

if i-CONV_INTEGER(A) then Y(i) <- '1'; end if;

end loop;

end if;

end process;

end Y3to8dec_c;

```

May not be synthesizable, or may have a slow or inefficient realization. But just fine for simulation and verification.

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

```

```

--Declaration of the module's inputs and outputs

entity fewgates is port (

A: in std_logic;

B: in std_logic;

C: in std_logic;

Y: out std_logic );

end fewgates;

```

--Defining the modules behavior Architecture behavioral of fewgates is begin process (A, B, C) begin Y <= C OR ((NOT A) AND (NOT B));

end process;

end behavioral;

# More VHDL

Powerful facilities for generating iterative circuit descriptions (e.g., multiplier array)

Facilities for modeling timing behavior of known components

Program I/O facilities for use in simulation

Design-management facilities for selecting alternative components and architectures

And more...