# Combinatorial Logic Design Principles

ECGR2181 Chapter 4 Notes

Reading: Chapter 4

## Boolean algebra

a.k.a. "switching algebra"

- deals with boolean values -- 0, 1

Positive-logic convention

analog voltages LOW, HIGH --> 0, 1

Negative logic -- seldom used

Signal values denoted by variables (X, Y, FRED, etc.)

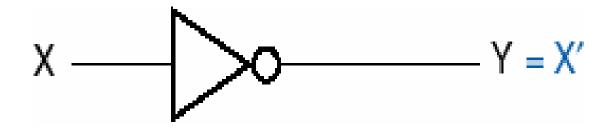

## **Boolean operators**

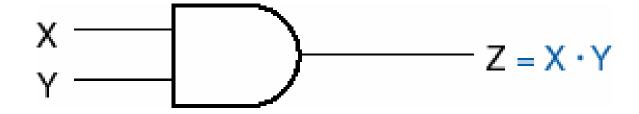

Complement:X' (opposite of X)

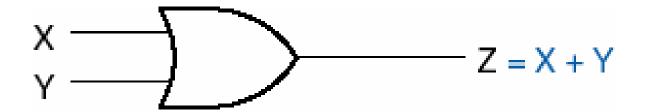

AND: X · Y

OR: X + Y

X + Y binary operators, described functionally by truth table.

| Χ   | Υ | X AND Y | Х | Υ | X OR Y | ' | Χ | NOT X |

|-----|---|---------|---|---|--------|---|---|-------|

| 0   | 0 | 0       | 0 | 0 | 0      |   | 0 | 1     |

| 0   | 1 | 0       | 0 | 1 | 1      |   | 1 | 0     |

| 1   | 0 | 0       | 1 | 0 | 1      |   |   |       |

| , 1 | 1 | 1       | 1 | 1 | 1      |   |   |       |

#### More definitions

Literal: a variable or its complement

- X, X', FRED', CS\_L

Expression: literals combined by

AND, OR, parentheses, complementation

- -X+Y

- $-P\cdot Q\cdot R$

- $-A+B\cdot C$

- $((FRED \cdot Z') + CS_L \cdot A \cdot B' \cdot C + Q5) \cdot RESET'$

Equation: Variable = expression

$- P = ((FRED \cdot Z') + CS_L \cdot A \cdot B' \cdot C + Q5) \cdot RESET'$

## **Logic symbols**

#### **Theorems**

(T1)

$$X + 0 = X$$

(T1')

$X \cdot 1 = X$

(Identities)

(T2)

$X + 1 = 1$

(T2')

$X \cdot 0 = 0$

(Null elements)

(T3)

$X + X = X$

(T3')

$X \cdot X = X$

(Idempotency)

(T4)

(X')' = X

(Involution)

(T5)

$X + X' = 1$

(T5')

$X \cdot X' = 0$

(Complements)

Proofs by perfect induction

#### **More Theorems**

$$(T6) X + Y = Y + X$$

$$(T6')$$

$X \cdot Y = Y \cdot X$

(Commutativity)

(T7)

$$(X + Y) + Z = X + (Y + Z)$$

$$(T7') \qquad (X \cdot Y) \cdot Z = X \cdot (Y \cdot Z)$$

(Associativity)

(T8)

$$X \cdot Y + X \cdot Z = X \cdot (Y + Z)$$

$$(X + Y) \cdot (X + Z) = X + Y \cdot Z$$

(Distributivity)

$$(T9) X + X \cdot Y = X$$

$$(T9')$$

$X \cdot (X + Y) = X$

(Covering)

(T10)

$$X \cdot Y + X \cdot Y' = X$$

$$(T10') \quad (X+Y) \cdot (X+Y') = X$$

(Combining)

(T11)

$$X \cdot Y + X' \cdot Z + Y \cdot Z = X \cdot Y + X' \cdot Z$$

(Consensus)

(T11')

$$(X + Y) \cdot (X' + Z) \cdot (Y + Z) = (X + Y) \cdot (X' + Z)$$

#### **N-variable Theorems**

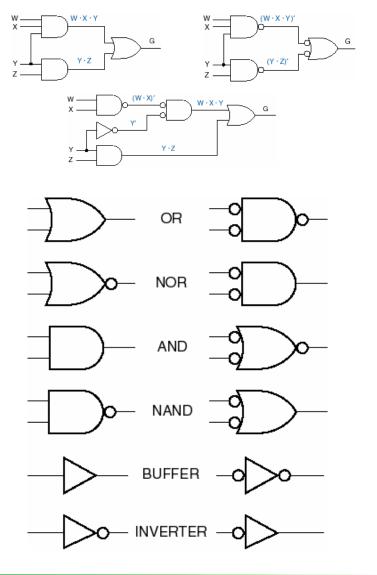

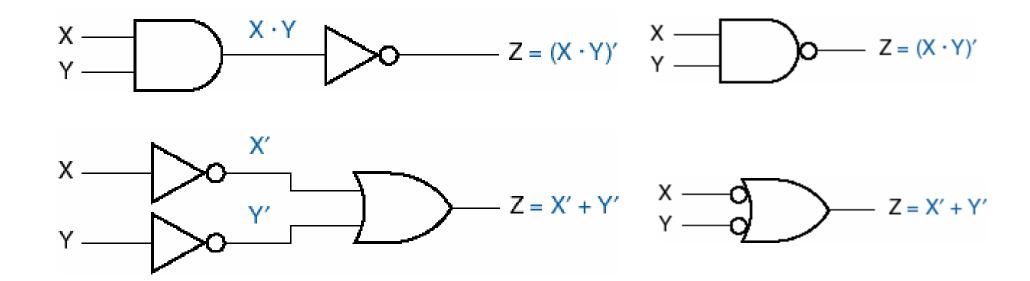

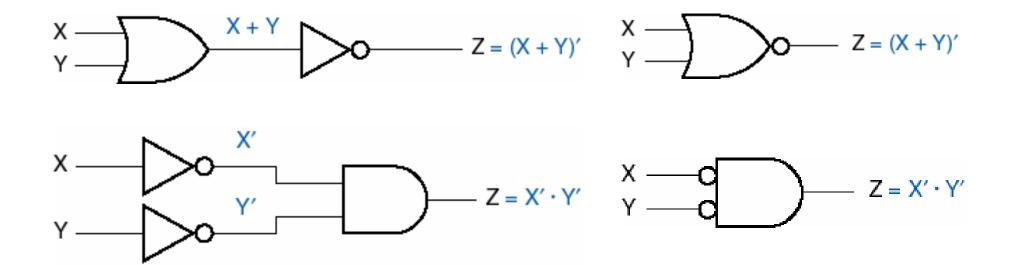

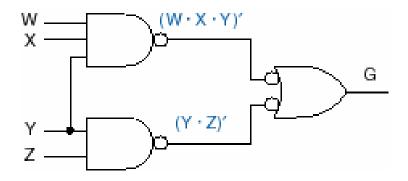

## **DeMorgan Symbol Equivalence**

#### Likewise for OR

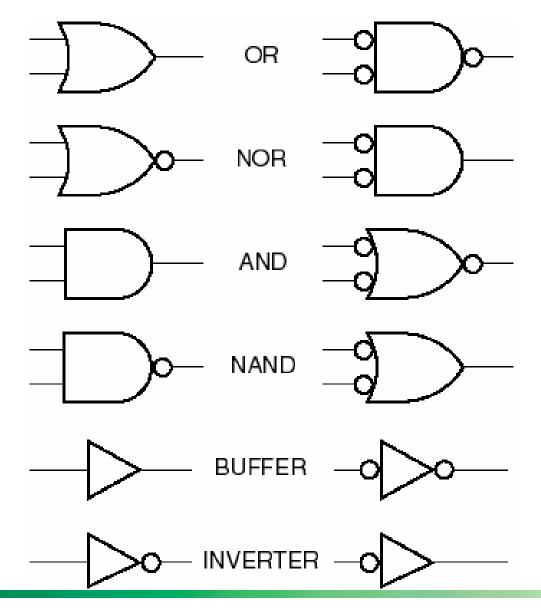

## **DeMorgan Symbols**

## Even more definitions (Sec. 4.1.6)

Product term

Sum-of-products expression

Sum term

Product-of-sums expression

Normal term

Minterm (n variables)

Maxterm (n variables)

## **Example Using 5 forms of a Logic Expression**

#### 1) The Truth Table:

| X | Υ | F |  |

|---|---|---|--|

| 0 | 0 | 1 |  |

| 0 | 1 | 0 |  |

| 1 | 0 | 0 |  |

| 1 | 1 | 1 |  |

- 2) **Sum-of-Products**: algebraic sum of minterms.  $F = X' \cdot Y' + X \cdot Y$

- 3) **Minterm List**: using  $\Sigma$  notation.  $F = \Sigma_{XY}(0,3)$

- 4) **Product-of-Sums**: algebraic product of maxterms.  $F = (X + Y') \cdot (X' + Y)$

- 5) **Maxterm List**: using  $\prod$  notation.  $F = \prod_{XY} (1,2)$

- Circuit is an Exclusive-NOR gate. A.K.A. an equivalence gate.

- F1 = F2

## Truth table vs. minterms & maxterms

| Row | Χ | Υ | Z | F        | Minterm                               | Maxterm     |

|-----|---|---|---|----------|---------------------------------------|-------------|

| 0   | 0 | 0 | 0 | F(0,0,0) | $X' \cdot Y' \cdot Z'$                | X + Y + Z   |

| 1   | 0 | 0 | 1 | F(0,0,1) | $X' \cdot Y' \cdot Z$                 | X + Y + Z'  |

| 2   | 0 | 1 | 0 | F(0,1,0) | $X^{\prime}\!\cdot Y\cdot Z^{\prime}$ | X + Y' + Z  |

| 3   | 0 | 1 | 1 | F(0,1,1) | $X' \cdot Y \cdot Z$                  | X + Y' + Z' |

| 4   | 1 | 0 | 0 | F(1,0,0) | $X \cdot Y' \cdot Z'$                 | X' + Y + Z  |

| 5   | 1 | 0 | 1 | F(1,0,1) | $X \cdot Y' \cdot Z$                  | X'+Y+Z'     |

| 6   | 1 | 1 | 0 | F(1,1,0) | $X \cdot Y \cdot Z'$                  | X'+Y'+Z     |

| 7   | 1 | 1 | 1 | F(1,1,1) | $X\cdot Y\cdot Z$                     | X'+Y'+Z'    |

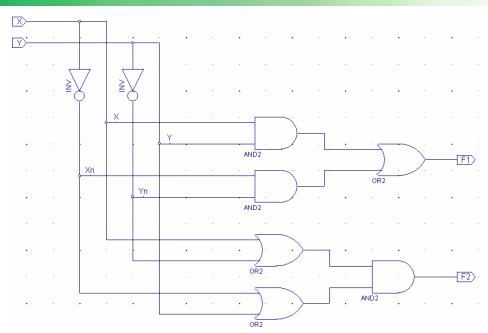

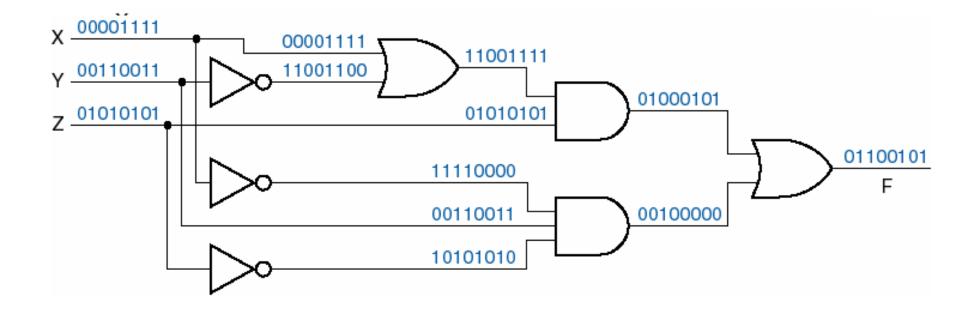

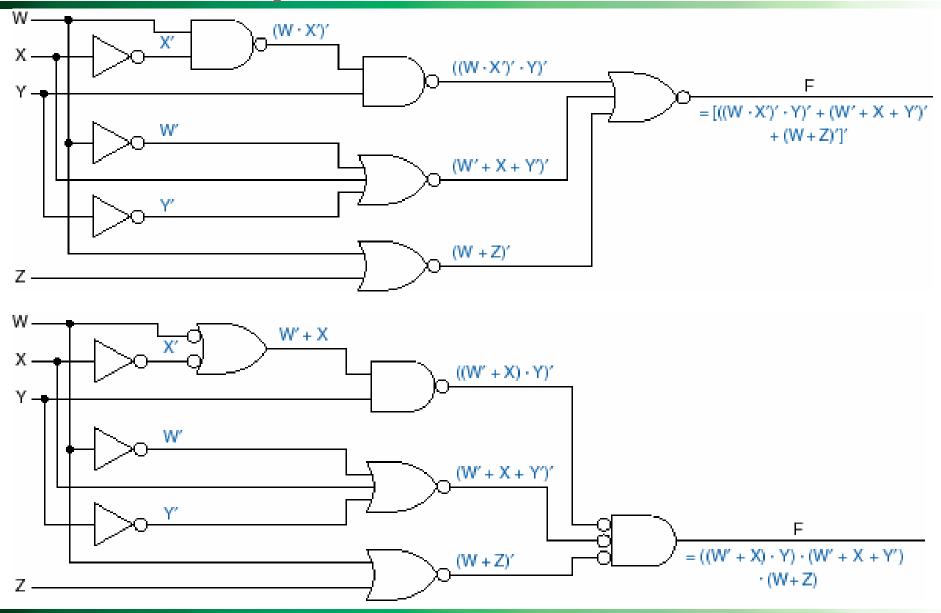

## **Combinational analysis**

## Signal expressions

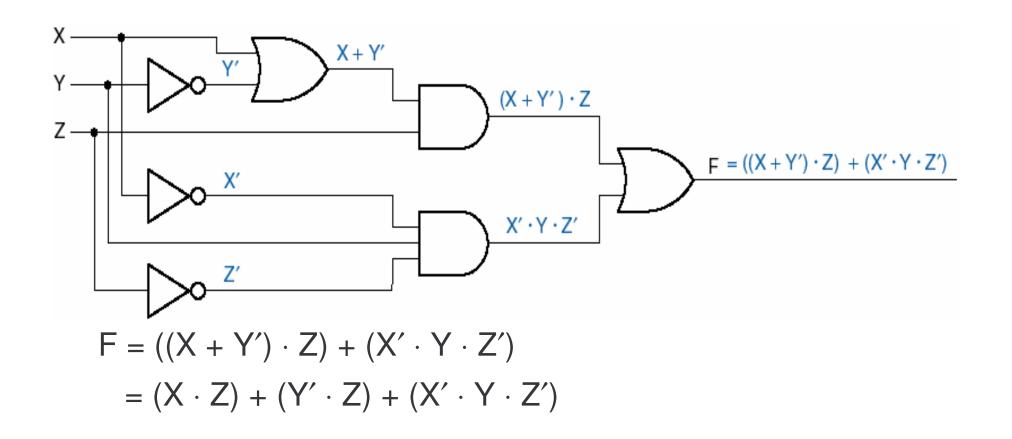

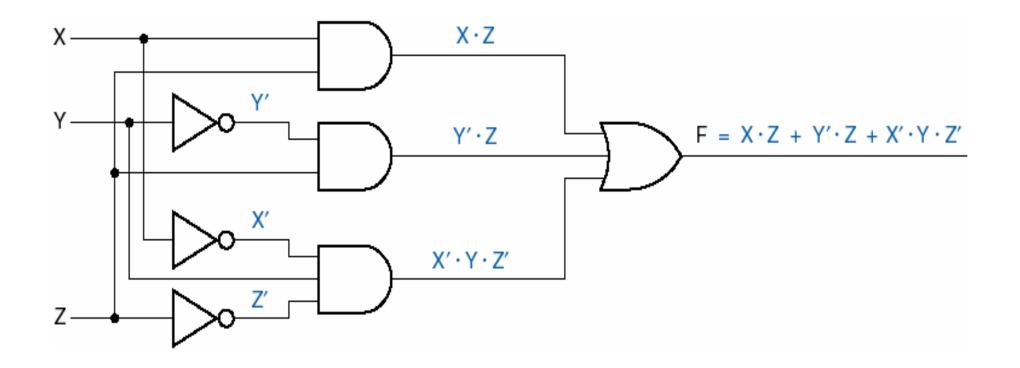

## New circuit, same function

## "Add out" logic function

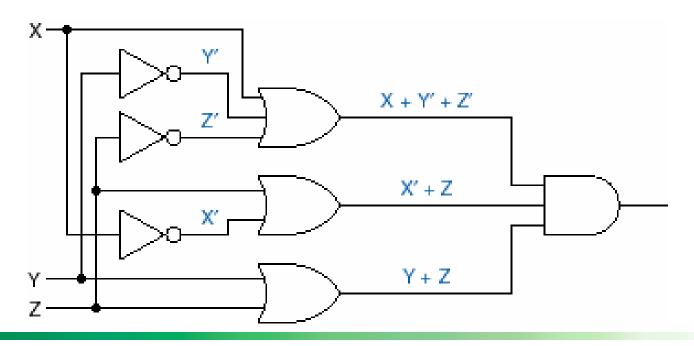

$$\begin{aligned} F &= ((X + Y') \cdot Z) + (X' \cdot Y \cdot Z') \\ &= (X + Y' + X') \cdot (X + Y' + Y) \cdot (X + Y' + Z') \cdot (Z + X') \cdot (Z + Y) \cdot (Z + Z') \\ &= 1 \cdot 1 \cdot (X + Y' + Z') \cdot (X' + Z) \cdot (Y + Z) \cdot 1 \\ &= (X + Y' + Z') \cdot (X' + Z) \cdot (Y + Z) \end{aligned}$$

#### Circuit:

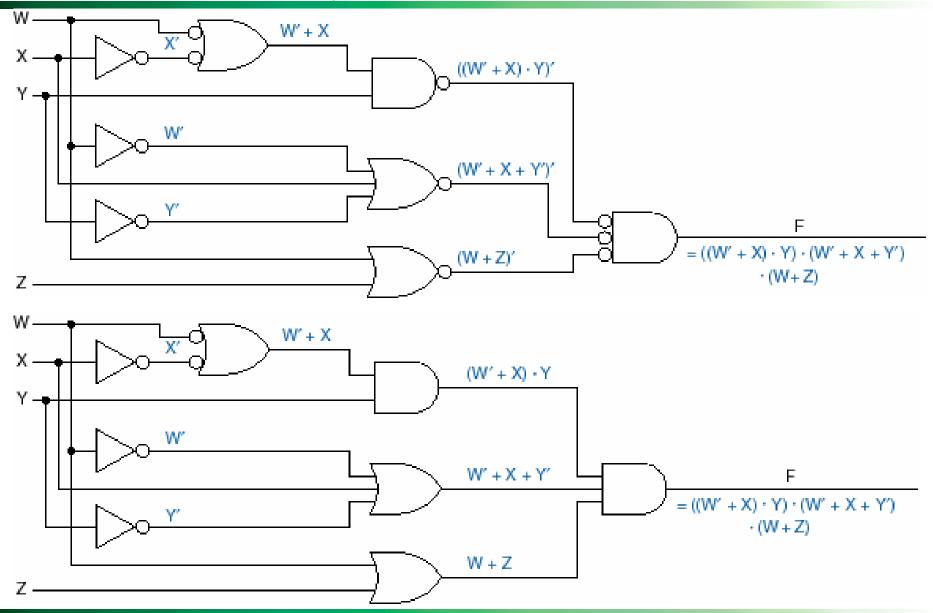

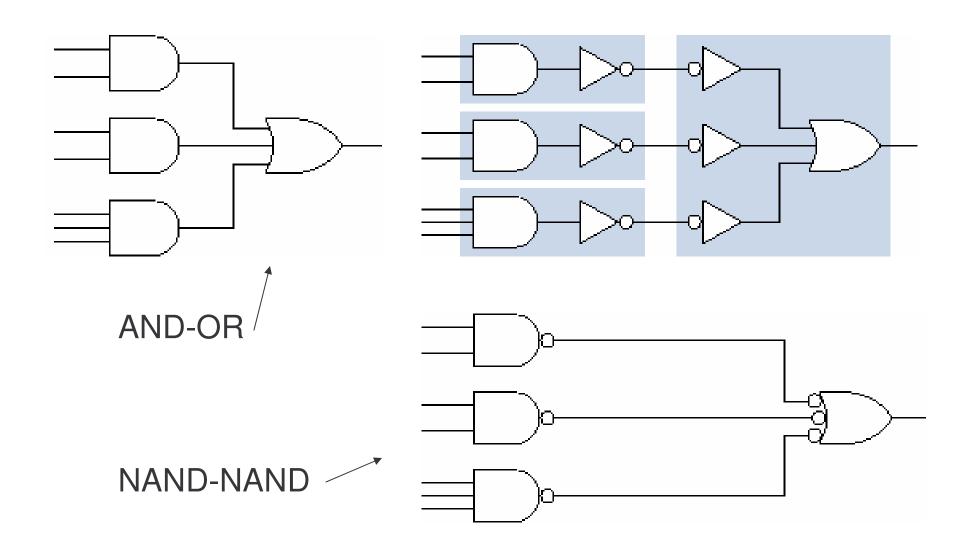

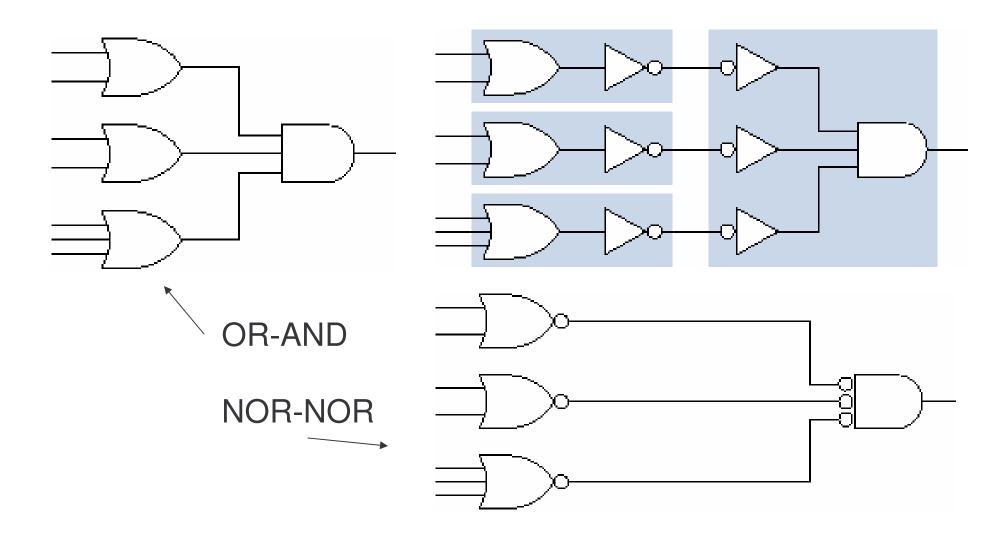

## **Shortcut: Symbol substitution**

## Different circuit, same function

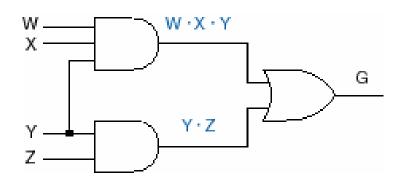

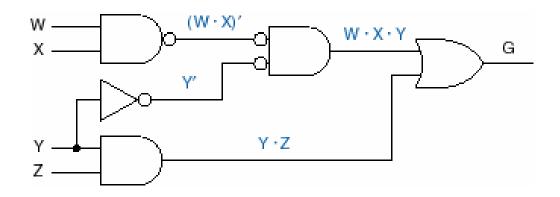

$$G(W, X, Y, Z) = W \cdot X \cdot Y + Y \cdot Z$$

## **Combinational-Circuit Analysis**

Combinational circuits -- outputs depend only on current inputs (not on history).

#### Kinds of combinational analysis:

- exhaustive (truth table)

- algebraic (expressions)

- simulation / test bench

- Write functional description in HDL

- Define test conditions / test vecors

- Compare circuit output with functional description (or knowngood realization)

## **Combinational-Circuit Design**

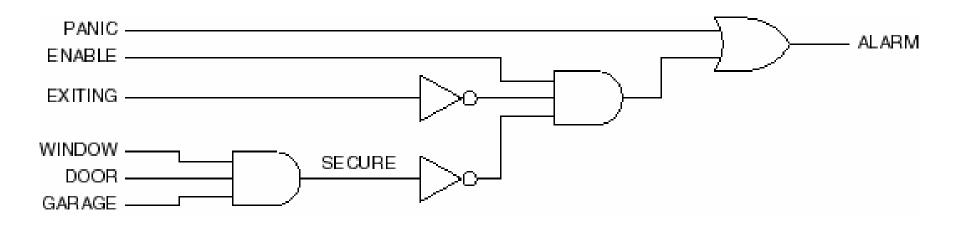

Sometimes you can write an equation or equations directly. Example (alarm circuit):

```

ALARM = PANIC + ENABLE · EXITING' · SECURE'

SECURE = WINDOW · DOOR · GARAGE

ALARM = PANIC + ENABLE · EXITING' · (WINDOW · DOOR · GARAGE)'

```

#### Corresponding circuit:

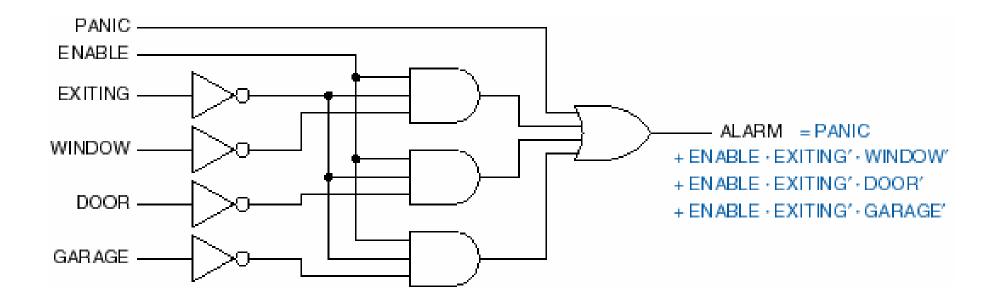

#### **Alarm-circuit transformation**

#### Sum-of-products form

Useful for programmable logic devices

#### "Multiply out":

## **Sum-of-products form**

## **Product-of-sums form**

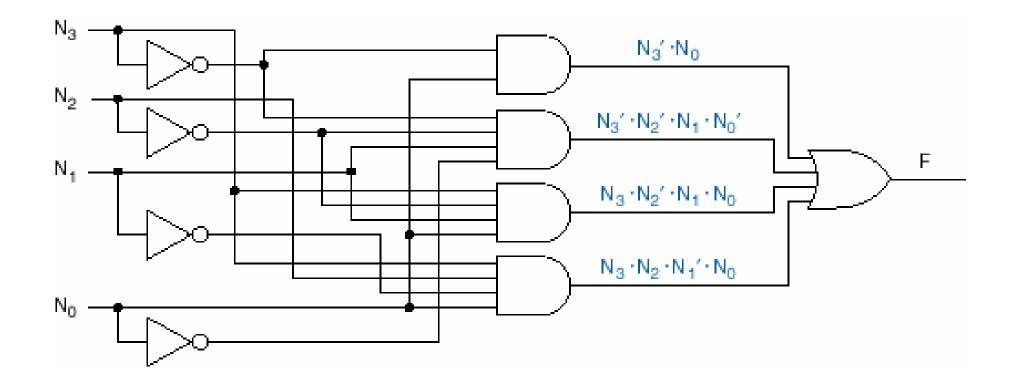

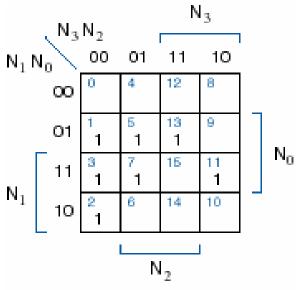

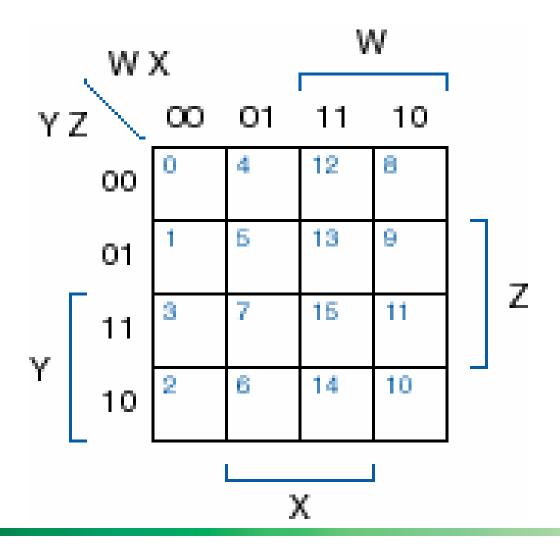

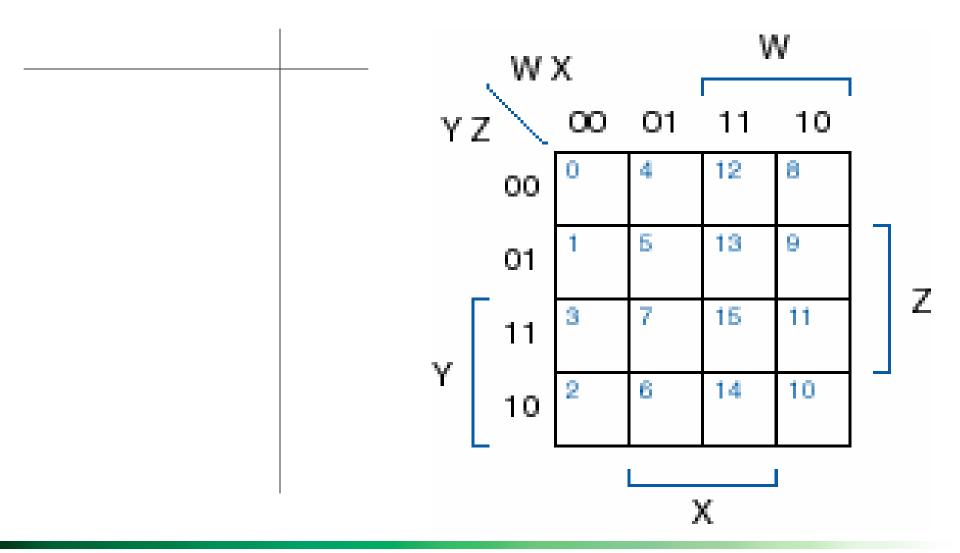

#### Brute-force design row $N_3 N_2 N_1 N_0$ () Truth table --> 0 canonical sum (sum of minterms) Example: prime-number detector - 4-bit input, $N_3N_2N_1N_0$ 0 9 0 10 0 $F = \Sigma_{N3N2N1N0}(1,2,3,5,7,11,13)$ 12 13

#### Minterm list --> canonical sum

$F = \Sigma_{N_*N_2,N_1,N_0}(1,2,3,5,7,11,13)$  $= N_3' \cdot N_2' \cdot N_1' \cdot N_0 + N_3' \cdot N_2' \cdot N_1 \cdot N_0' + N_3' \cdot N_2' \cdot N_1 \cdot N_0 + N_3' \cdot N_2 \cdot N_1' \cdot N_0$  $+ N_3' \cdot N_2 \cdot N_1 \cdot N_0 + N_3 \cdot N_2' \cdot N_1 \cdot N_0 + N_3 \cdot N_2 \cdot N_1' \cdot N_0$  $N_3' \cdot N_2' \cdot N_4' \cdot N_0$  $N_3$  $N_3' \cdot N_2' \cdot N_1 \cdot N_0'$  $N_2$  $N_3' \cdot N_2' \cdot N_4 \cdot N_0$  $N_2$  $N_3' \cdot N_2 \cdot N_1' \cdot N_0$ F  $N_{\rm d}$  $N_3' \cdot N_2 \cdot N_1 \cdot N_0$  $N_1'$  $N_3 \cdot N_2' \cdot N_1 \cdot N_0$  $N_0$  $N_3 \cdot N_2 \cdot N_4' \cdot N_0$  $N_0$

## Algebraic simplification

Theorem T8,

$$X \cdot Y + X \cdot Y' = X$$

$$F = \Sigma_{N_3,N_2,N_1,N_0}(1, 3, 5, 7, 2, 11, 13)$$

$$= \ N_3' \cdot N_2' N_1' N_0 + N_3' \cdot N_2' \cdot N_1 \cdot N_0 + N_3' \cdot N_2 \cdot N_1' \cdot N_0 + N_3' \cdot N_2 \cdot N_1 \cdot N_0 + \dots$$

$$= (N_3' \cdot N_2' \cdot N_1' \cdot N_0 + N_3' \cdot N_2' \cdot N_1 \cdot N_0) + (\cdot N_3' \cdot N_2 \cdot N_1' \cdot N_0 + N_3' \cdot N_2 \cdot N_1 \cdot N_0) + \dots$$

$$= N_3'N_2' \cdot N_0 + N_3' \cdot N_2 \cdot N_0 + \dots$$

Reduce number of gates and gate inputs

## Resulting circuit

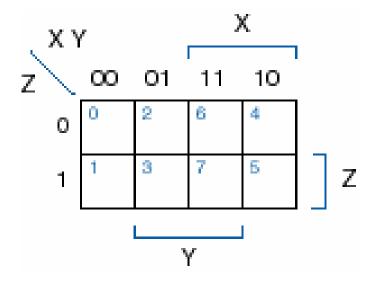

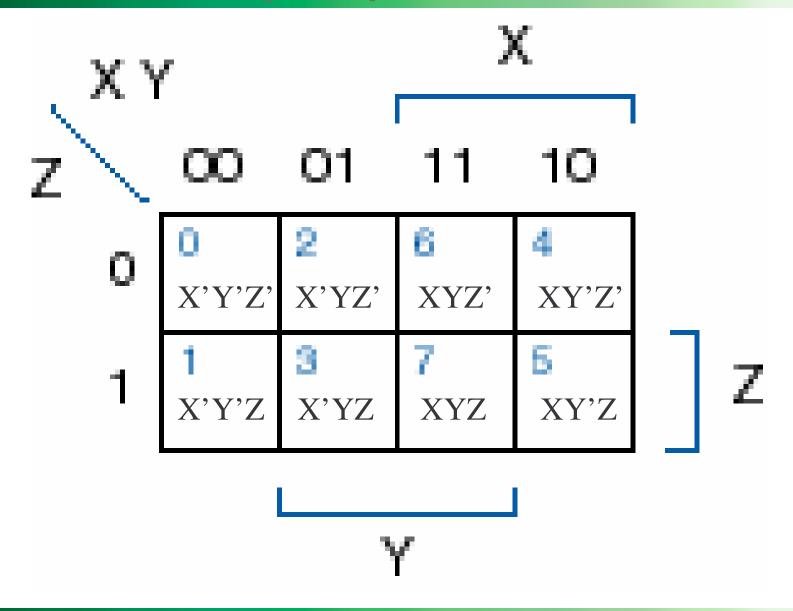

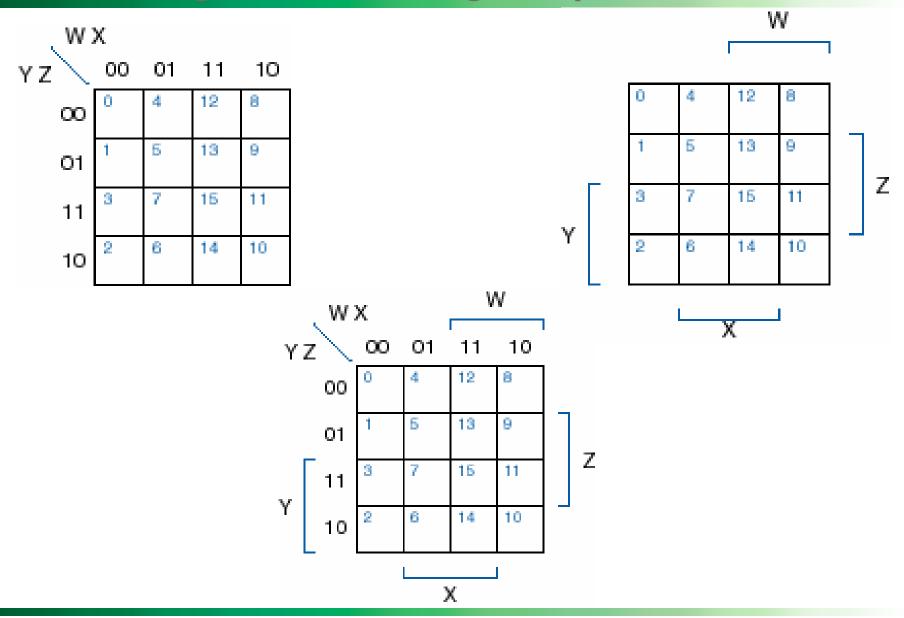

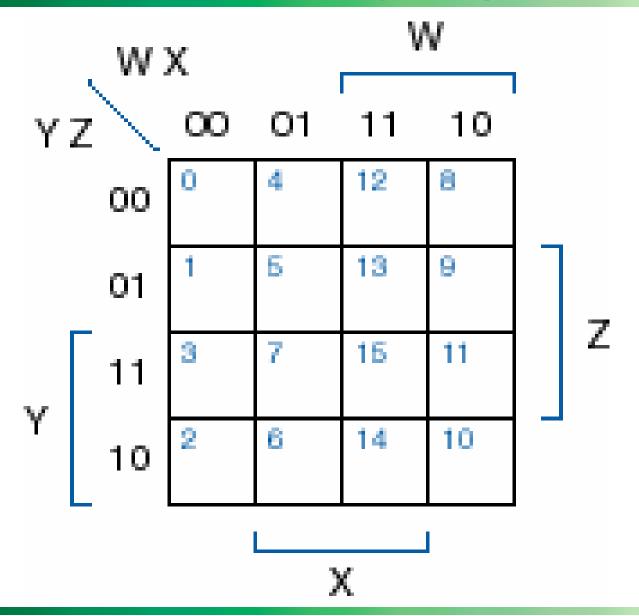

## 3-variable Karnaugh map

## 3-variable Karnaugh map

## Visualizing T10 -- Karnaugh maps

## Visualizing T10 -- Karnaugh maps

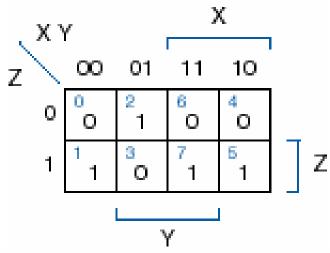

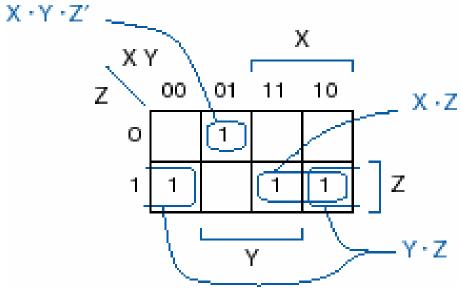

# **Example:** $F = \Sigma(1,2,5,7)$

| Х | Υ | Z | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

## Karnaugh-map usage

Plot 1s corresponding to minterms of function.

Circle largest possible rectangular sets of 1s.

- # of 1s in set must be power of 2

- OK to cross edges

Read off product terms, one per circled set.

- Variable is 1 ==> include variable

- Variable is 0 ==> include complement of variable

- Variable is both 0 and 1 ==> variable not included

Circled sets and corresponding product terms are called "prime implicants"

Minimum number of gates and gate inputs

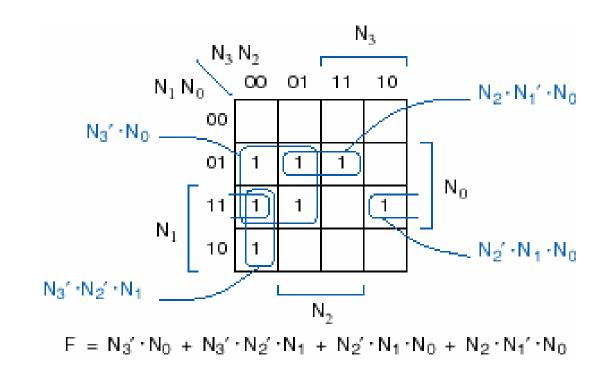

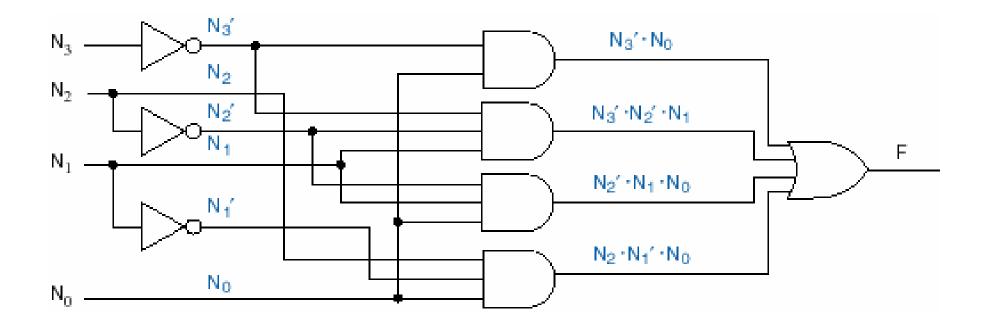

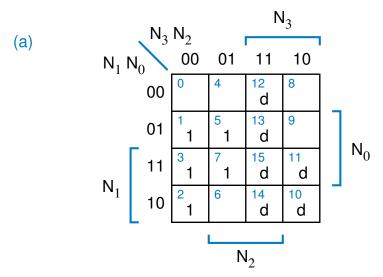

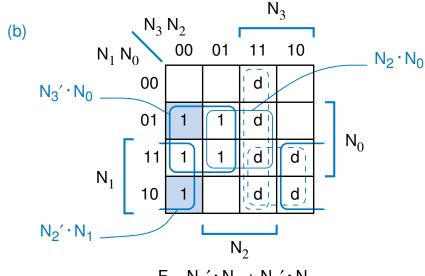

#### Prime-number detector

$F = \Sigma_{N3,N2,N1,N0}(1,2,3,5,7,11,13)$

## Resulting Circuit.

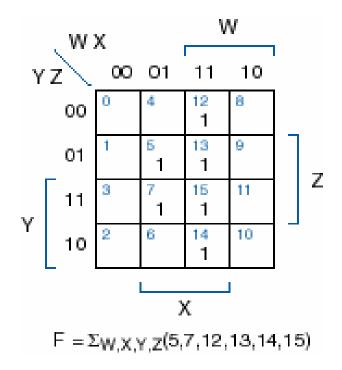

## Yet another example

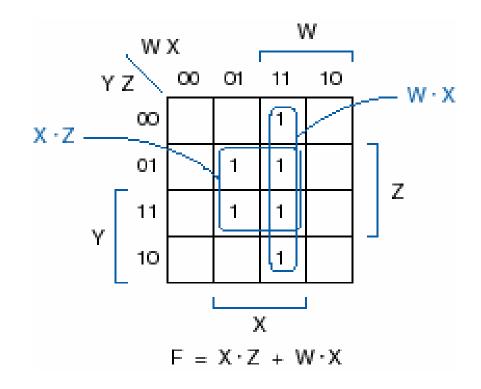

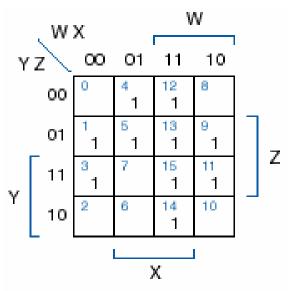

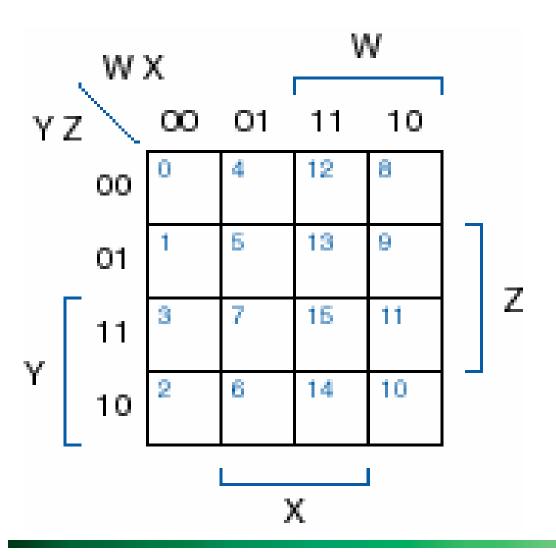

$F = \Sigma_{W,X,Y,Z}(1,3,4,5,9,11,12,13,14,15)$

Distinguished 1 cells

Essential prime implicants

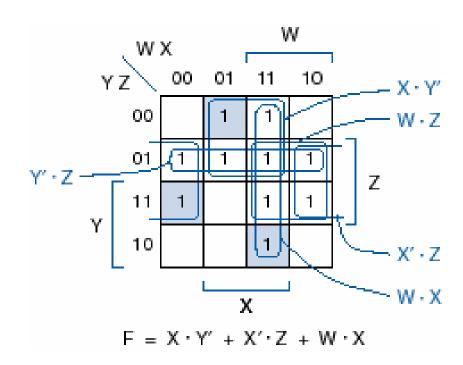

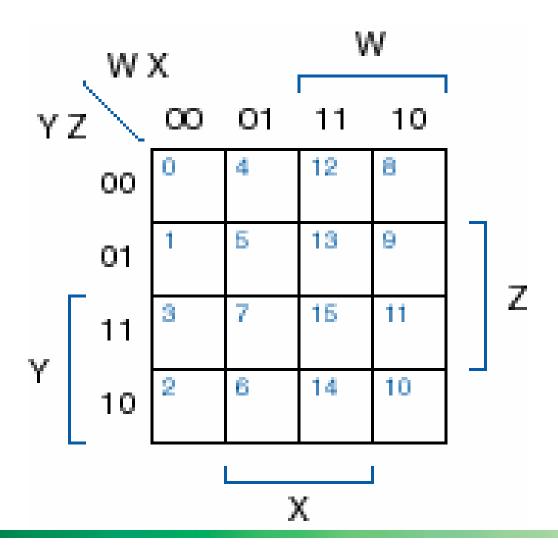

$F(W,X,Y,Z) = \Sigma m(0,1,2,4,5,6,8,9,12,13,14)$

$F(W,X,Y,Z) = \Sigma m(0,1,2,3,6,8,9,10,11,14)$

#### **Don't Cares**

Copyright © 2000 by Prentice Hall, Inc. Digital Design Principles and Practices, 3/e

$\mathsf{F} = \Sigma_{\mathsf{N3},\mathsf{N2},\mathsf{N1},\mathsf{N0}}(1,\!2,\!3,\!5,\!7) + \mathsf{d}(10,\!11,\!12,\!13,\!14,\!15)$

$$F = N_3' \cdot N_0 + N_2' \cdot N_1$$

$F(W,X,Y,Z) = \sum m(0,1,2,3,6,8,9,10,11,14) + d(7,15)$

## **Current Logic Design**

Lots more than 6 inputs -- can't use Karnaugh maps

Use software to synthesize logic expressions and

minimize logic

Hardware Description Languages -- VHDL and Verilog