# Embedded Systems: An Introduction using the Renesas RX63N Microcontroller

BY JAMES M. CONRAD

Micriµm Press 1290 Weston Road, Suite 306 Weston, FL 33326 USA

www.micrium.com

Designations used by companies to distinguish their products are often claimed as trademarks. In all instances where Micriµm Press is aware of a trademark claim, the product name appears in initial capital letters, in all capital letters, or in accordance with the vendor's capitalization preference. Readers should contact the appropriate companies for more complete information on trademarks and trademark registrations. All trademarks and registered trademarks in this book are the property of their respective holders.

Copyright © 2013 by James M. Conrad except where noted otherwise. Published by Micriµm Press. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of the publisher; with the exception that the program listings may be entered, stored, and executed in a computer system, but they may not be reproduced for publication.

The programs and code examples in this book are presented for instructional value. The programs and examples have been carefully tested, but are not guaranteed to any particular purpose. The publisher and content contributors do not offer any warranties and does not guarantee the accuracy, adequacy, or completeness of any information herein and is not responsible for any errors or omissions. The publisher and content contributors assume no liability for damages resulting from the use of the information in this book or for any infringement of the intellectual property rights of third parties that would result from the use of this information.

Library of Congress subject headings:

- 1. Embedded computer systems

- 2. Real-time data processing

- 3. Computer software—Development

For bulk orders, please contact Micrium Press at: +1 954 217 2036

ISBN: 978-1-935772-94-1

Please report errors or forward any comments and suggestions to jmconrad@uncc.edu.

# Preface

This book is the results of a long relationship the author has enjoyed with Renesas Electronics America, Inc. (and one of its predecessors, Mitsubishi Electronics). I originally worked with this company because of their commitment to providing a low-cost evaluation board and free development software that students could purchase and use in classes and senior design projects. Over the years the boards have remained as affordable (and popular) as ever, and the software development tools available have added more functionality while still remaining available for free to our students.

I have been teaching embedded systems courses for over fourteen years (and working in the field even longer). I had not been able to find a book suitable for using in an undergraduate course that would lend itself to the theoretical and applied nature of embedded systems design. Renesas had been asking me to create a book for several years, and the introduction of the new RX63N microcontroller offered a wonderful opportunity to work with this powerful device and integrate it into classes.

This book also has a radical feature not seen in many books currently on the market (if any). It is freely available for download and is also provided with the Renesas RX63N evaluation board. It is also available for purchase in hardcopy form for a modest price.

This book can be used on its own for an Introduction to Embedded Systems class or an Introduction to Microprocessors/Microcontrollers. It can also be used as a supplement in many different types of classes. The book also has supplemental materials available through Renesas Electronics America's University program. These materials include homework solutions (sorry, faculty only!), PowerPoint presentations, lab exercises, and a test bank. Video lectures can be found on YouTube under the channel stiquitojmconrad.

This book would not have been possible had it not been for the assistance of numerous people. Several students and educators contributed to some of the chapters in the RX63N (original) version of the book, including: Adam Harris (1, 2), Suganya Jebasingh (2, 6), Vikram Gill (3,4), Archana Subramanian (4), Onkar Raut (5, 7), Steven Erdmanczyk (8,9), Sunil Gurram (8), Vivek Srikantan (10), and Paul Mohan Das (10). Alex Dean of North Carolina State University heavily edited the original book and was it's co-author. Stephanie Conrad heavily edited versions of the chapters. Michael McLain and Sam Shue helped create the solutions for the homework assignments. Kunal Bagewadi, Robin Davidsson, and Amogh Gokhale went through the original RX62N book and made corrections to text and code examples to convert it to the RX63N microcontroller and evaluation board. Thanks go to the compositor, Linda Foegen, and especially to June Hay-Harris, Rob Dautel, and Todd DeBoer of Renesas for their help in getting this book produced and published (and for their patience!). Many, many thanks go to the reviewers who offered valuable suggestions to

make this book better, especially David Brown, Jerry Zacharias, Mitch Ferguson, Mike Wilkinson, John A. Onuska, Mark Radley, Barry Williams, and students from my UNC Charlotte Embedded Systems courses.

I would like to personally thank my parents, the Conrads, and my in-laws, the Warrens, for their continued assistance and guidance through the years while I worked on this and other books. Also, I would especially like to thank my children, Jay, Mary Beth, and Caroline, and my wife Stephanie, for their understanding when I needed to spend more time on the book than I spent with them.

James M. Conrad September 2013

# Foreword

The world of MCU-based embedded designs can be divided into those that take advantage of existing code and MCUs, and those that require leading edge MCU architectures and implementations. Dr. Conrad spent more than a year internalizing the inner workings and surrounding ecosystem of the newly-developed RX architecture, and has generated a book showcasing the RX line which has a level of peripheral integration that has not been seen before. Indeed, by taking the best DNA of both CISC and RISC architectures, and combining them into a new breed of MCU, the RX line enables design approaches that were previously spread across the CISC and RISC camps and inaccessible in one device line.

The author leverages the capabilities of the RX and demonstrates his own expert grasp of all the dynamics that differentiate successful end solutions from those of the "me-too" variety. He recognizes that successful embedded systems require more than just good hardware and software engineering. Jim has masterfully applied RX capabilities to real world challenges using examples, applications, and approaches that will surely empower individuals and teams of designers.

Readers aspire to find books that have the right balance between depth and breadth. Where there is too much detail, the relevance can be obscured; while a broad brush approach may trivialize the essence of key topics. This is especially true of books relating to embedded designs that must achieve a utilitarian purpose. Here, Jim skillfully navigates from topic to topic, knowing exactly when to throttle for maximum utility.

Whether you are a university student preparing for the real world, a design engineer looking for leading edge approaches to time-critical processes, or a manager attempting to further your risk management techniques, you will find his approach to embedded systems to be stimulating and compelling.

> Ali Sebt Renesas September 19, 2013

# Contents

| Preface  | iii |

|----------|-----|

| Foreword | V   |

# **CHAPTER ONE**

| Intro | duction                         | to Embedded Systems                                   | 1 |

|-------|---------------------------------|-------------------------------------------------------|---|

| 1.1   | Learni                          | ng Objectives                                         | 1 |

| 1.2   | Conce                           | epts                                                  | 1 |

|       | 1.2.1                           | Economics and Microcontrollers                        | 1 |

|       | 1.2.2                           | Embedded Networks                                     | 2 |

| 1.3   | Туріса                          | l Benefits of Embedded Systems                        | 2 |

|       | 1.3.1                           | Greater Performance and Efficiency                    | 3 |

|       | 1.3.2                           | Lower Costs                                           | 3 |

|       | 1.3.3                           | More Features                                         | 4 |

|       | 1.3.4                           | Better Dependability                                  | 4 |

| 1.4   | Embeo                           | dded System Functions                                 | 4 |

| 1.5   | Attributes of Embedded Systems  |                                                       |   |

| 1.6   | Constraints on Embedded Systems |                                                       | 6 |

| 1.7   | Desigr                          | ning and Manufacturing Embedded Systems               | 6 |

| 1.8   | An Exa                          | ample of an Embedded System: The Renesas Sakura Board | 8 |

| 1.9   | Summ                            | ary of Book Contents                                  | 8 |

| 1.10  | Recap                           |                                                       | 8 |

| 1.11  | Refere                          | ences                                                 | 9 |

# **CHAPTER TWO**

| Conce | Concepts of Microcontrollers     |    |

|-------|----------------------------------|----|

| 2.1   | Learning Objectives              | 11 |

| 2.2   | Interfacing with Digital Signals | 11 |

CONTENTS

|     | 2.2.1   | General Purpose Digital I/O                                           | 11 |

|-----|---------|-----------------------------------------------------------------------|----|

|     |         | Port Direction Register (PDR)                                         | 12 |

|     |         | Set Switch 1 (Port 4 bit 0) as Input                                  | 13 |

|     |         | Port Output Data Register (PODR)                                      | 13 |

|     |         | Set LED1 (Port D bit 0) as Output                                     | 14 |

|     |         | Sets LEDs 1, 2, and 3 (Port D bit 0, 1, and 2) as Outputs             | 14 |

|     |         | Port Input Register (PIDR)                                            | 14 |

|     |         | Check State of Switch1 (Port 4 bit 0) and Turn On LED1 (Port D bit 0) | 15 |

|     |         | Port Mode Register (PMR)                                              | 15 |

|     |         | Open Drain Control Registers (ODR0/ODR1)                              | 15 |

|     |         | Pull-Up Resistor Control Register (PCR)                               | 15 |

|     |         | Drive Capacity Control Register (DSCR)                                | 16 |

|     | 2.2.2   | Example 1: Reading Switches to Control LEDs                           | 16 |

|     |         | Using LEDs as Outputs                                                 | 16 |

|     |         | Using Switches as Inputs                                              | 17 |

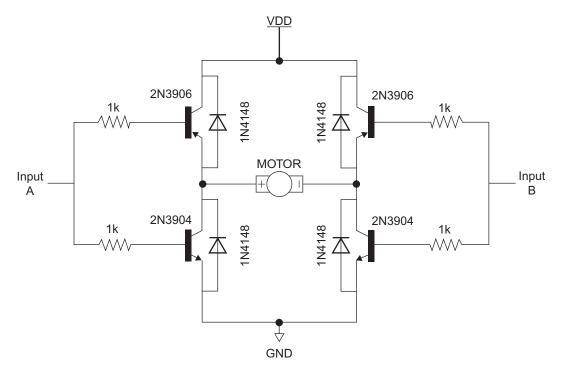

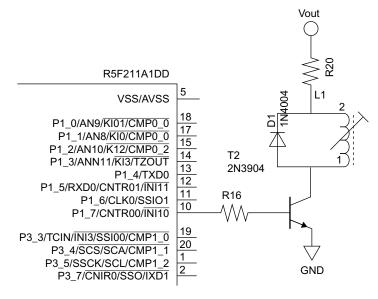

|     | 2.2.3   | Driving Motors and Coils                                              | 20 |

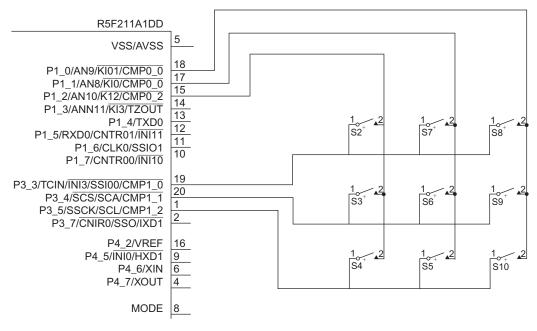

|     | 2.2.4   | Scanning Matrix Keypads                                               | 22 |

| 2.3 | Interfa | acing with Analog Signals                                             | 24 |

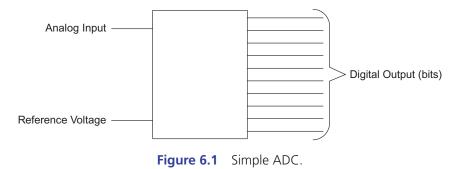

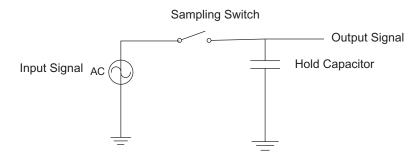

|     | 2.3.1   | Analog to Digital Converters                                          | 24 |

|     | 2.3.2   | Analog Comparator                                                     | 25 |

|     | 2.3.3   | Digital to Analog Conversion                                          | 26 |

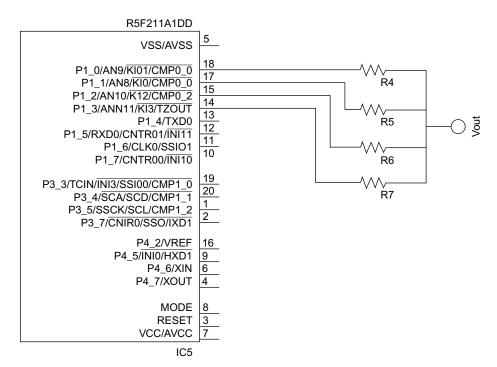

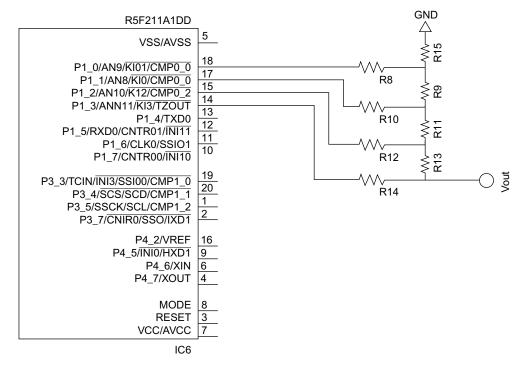

|     |         | Resistor Networks                                                     | 26 |

|     |         | Binary Weighted DACs                                                  | 26 |

|     |         | R-2R DAC                                                              | 27 |

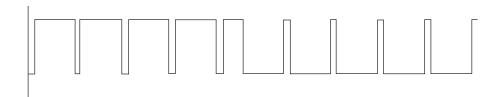

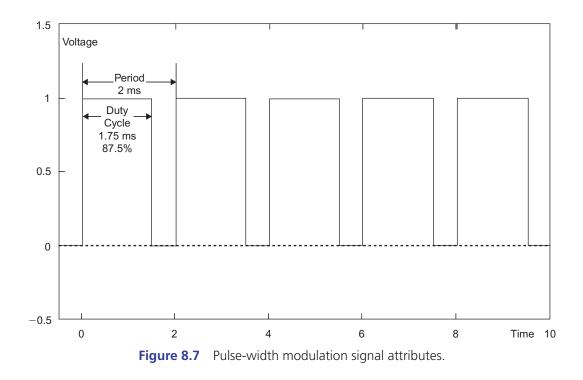

|     |         | Pulse Width Modulation                                                | 28 |

| 2.4 | Infrast | ructure: Power, Clock, and Reset                                      | 28 |

|     | 2.4.1   | Power Supply                                                          | 28 |

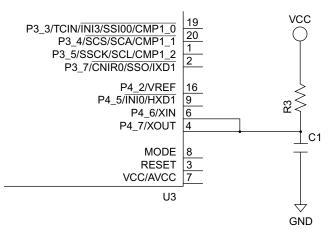

|     | 2.4.2   | Clock Signal Generation                                               | 30 |

|     | 2.4.3   | Reset Circuit                                                         | 31 |

| 2.5 | Recap   |                                                                       | 32 |

| 2.6 | Refere  | ences                                                                 | 32 |

| 2.7 | Exerci  | ses                                                                   | 32 |

### viii

| Orga | nizatio           | and Architecture of the Renesas RX63N Microcontroller Board | 35 |

|------|-------------------|-------------------------------------------------------------|----|

| 3.1  | Learni            | ng Objectives                                               | 35 |

| 3.2  | Basic Concepts    |                                                             | 35 |

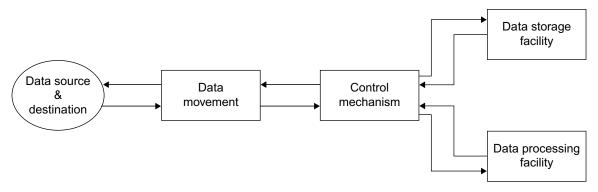

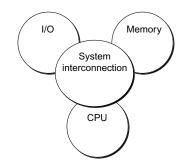

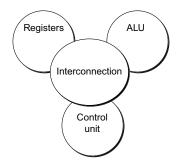

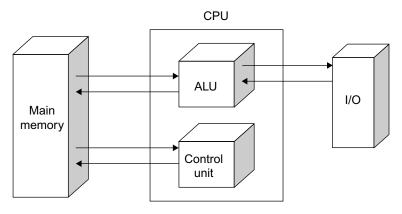

|      | 3.2.1             | Introduction to Computer Organization & Architecture        | 35 |

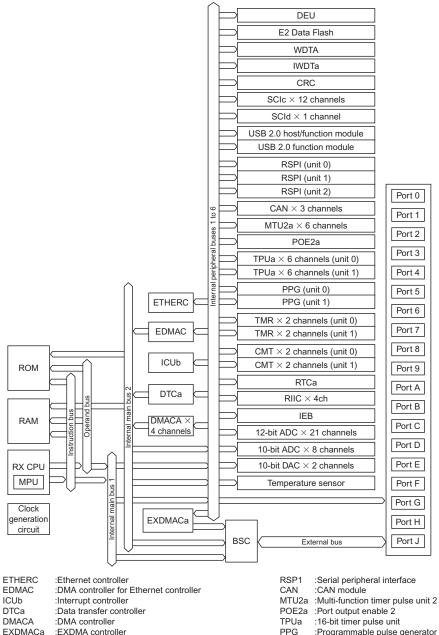

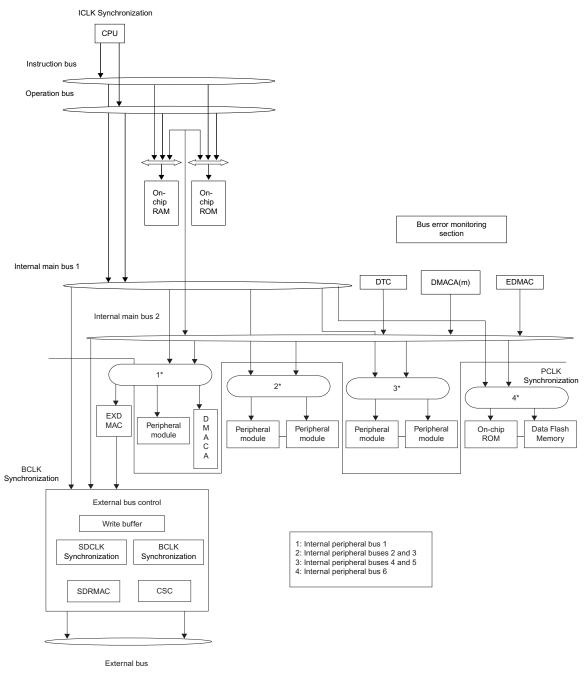

|      | 3.2.2             | Architecture of the Renesas RX63N                           | 38 |

|      |                   | CPU                                                         | 42 |

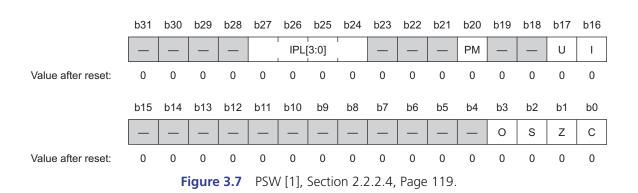

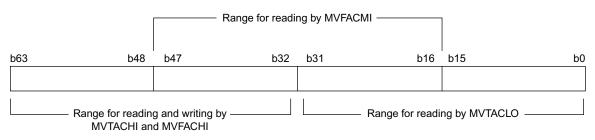

|      |                   | Register Set                                                | 42 |

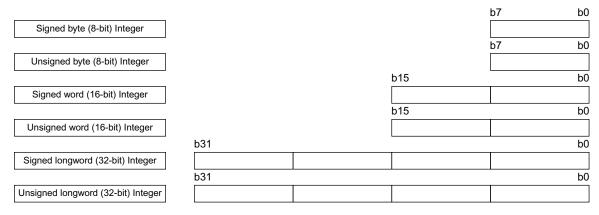

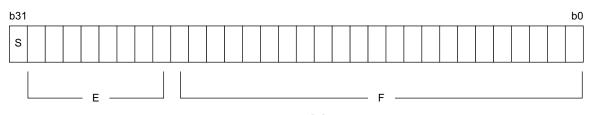

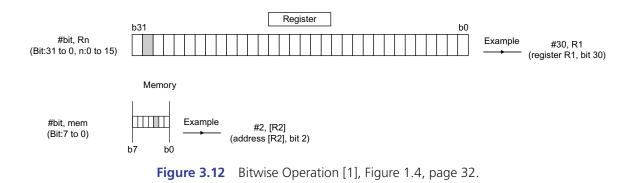

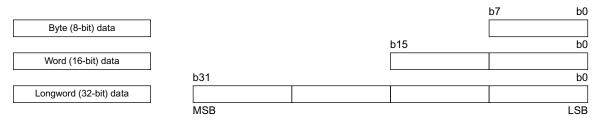

|      | 3.2.3             | Data Types                                                  | 52 |

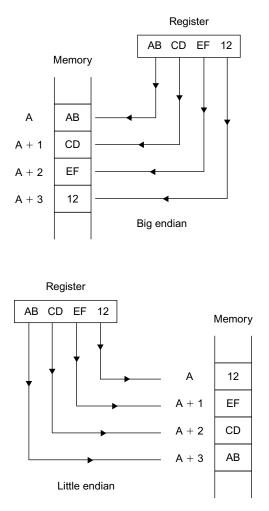

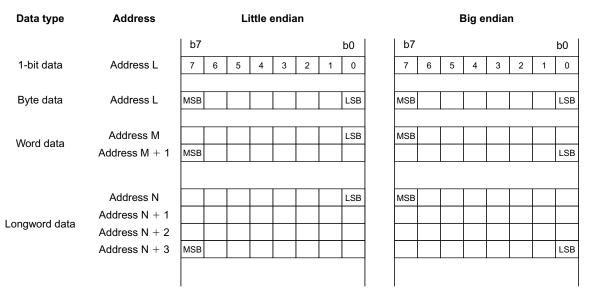

|      | 3.2.4             | Endianness                                                  | 55 |

|      | 3.2.5             | Data Arrangement                                            | 56 |

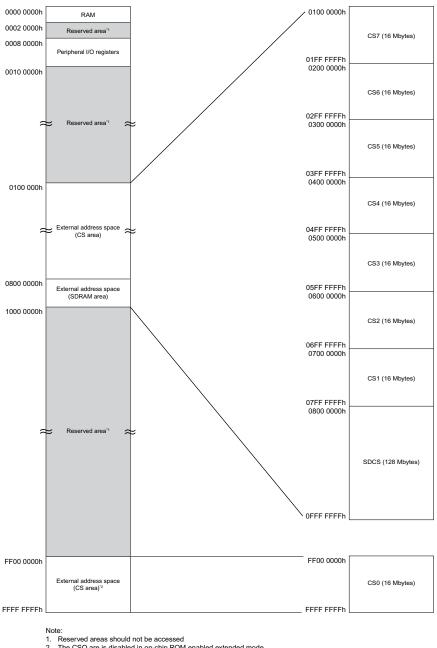

|      | 3.2.6             | Bus Specification                                           | 57 |

|      |                   | Description of Buses                                        | 58 |

|      |                   | Bus Error Monitoring Section                                | 63 |

|      |                   | Types of Bus Error                                          | 63 |

| 3.3  | Basic I           | Examples                                                    | 64 |

| 3.4  | Advanced Concepts |                                                             | 65 |

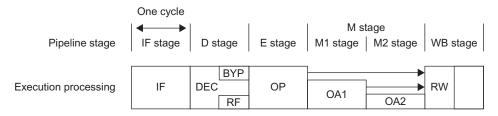

|      | 3.4.1             | Pipelining                                                  | 65 |

|      |                   | Pipeline Basic Operation                                    | 67 |

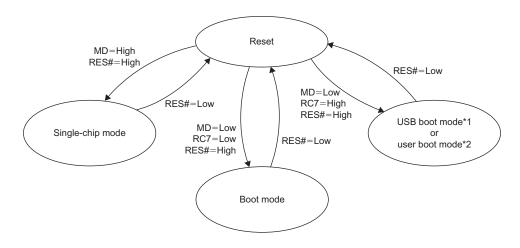

|      | 3.4.2             | Operating Modes                                             | 71 |

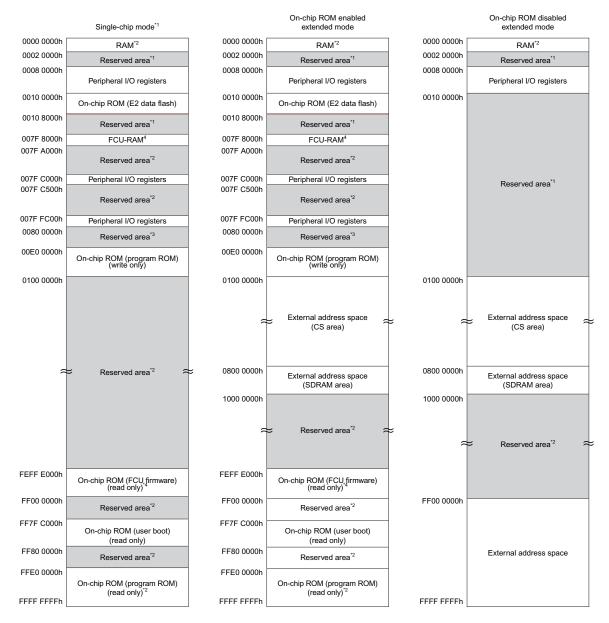

|      | 3.4.3             | Memory Organization                                         | 75 |

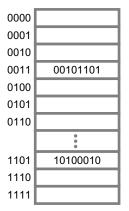

|      |                   | Byte Addressing vs. Word Addressing                         | 75 |

|      | 3.4.4             | Memory Map                                                  | 76 |

|      | 3.4.5             | I/O Registers                                               | 76 |

| 3.5  | Advar             | iced Examples                                               | 80 |

| 3.6  | Refere            | ences                                                       | 82 |

| 3.7  | Exercises         |                                                             | 82 |

# **x** Contents

# **CHAPTER FOUR**

| Software Development Tools |                   | 85                                                    |     |

|----------------------------|-------------------|-------------------------------------------------------|-----|

| 4.1                        | Learni            | ing Objectives                                        | 85  |

| 4.2                        | Basic (           | Concepts                                              | 85  |

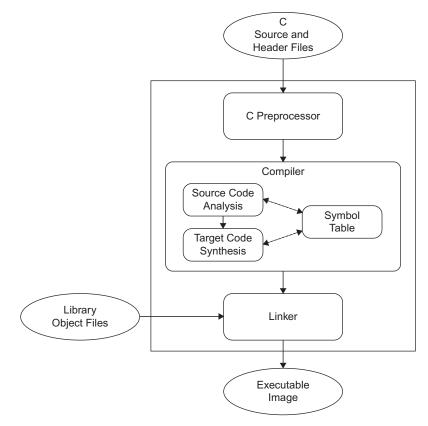

|                            | 4.2.1             | Compilation Mechanism                                 | 85  |

|                            | 4.2.2             | Compilers for Embedded Systems                        | 87  |

|                            | 4.2.3             | RX Compiler Package                                   | 87  |

|                            |                   | Features of RX Family C/C++ Compiler                  | 88  |

|                            | 4.2.4             | Debugging Tools                                       | 89  |

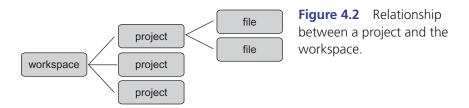

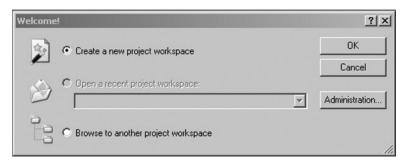

|                            | 4.2.5             | Introduction to HEW                                   | 89  |

|                            |                   | Creating or Opening a Project in HEW-IDE              | 90  |

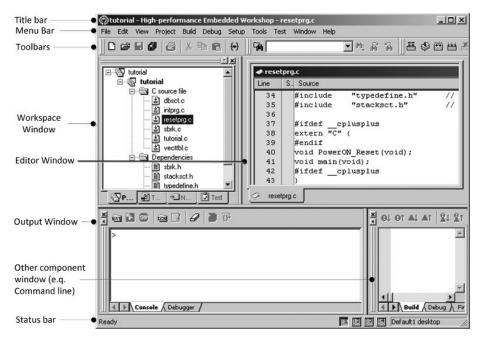

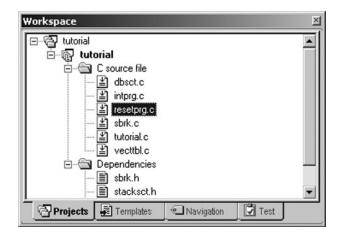

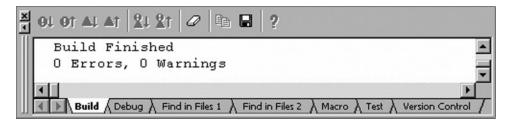

|                            |                   | Windows in HEW                                        | 92  |

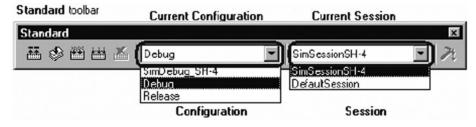

|                            |                   | Concept of Configuration and Session                  | 93  |

|                            |                   | Configuration                                         | 94  |

|                            |                   | Session                                               | 94  |

|                            | 4.2.6             | Concepts of Header Files                              | 94  |

|                            |                   | Header Files Used in RX Family C/C++ Compiler         | 95  |

|                            |                   | Header Files Associated with RX63N                    | 95  |

| 4.3                        | Basic I           | Examples                                              | 96  |

| 4.4                        | Advanced Concepts |                                                       | 105 |

|                            | 4.4.1             | Advanced Debugging Concepts                           | 105 |

|                            | 4.4.2             | The J-Link Debugger                                   | 116 |

|                            |                   | Features                                              | 117 |

|                            | 4.4.3             | Description of the Header Files Used in the RX Family | 117 |

| 4.5                        | Advar             | nced Examples                                         | 129 |

|                            |                   | Window Configuration                                  | 129 |

|                            |                   | Changing the Register Display Radix                   | 130 |

|                            |                   | Setting the Layout                                    | 130 |

|                            |                   | Choosing a Register to be Displayed                   | 132 |

|                            |                   | Modifying the Register Contents                       | 132 |

|                            |                   | Setting the Flag Value                                | 133 |

| Contents | xi |

|----------|----|

| Contents | х  |

| Screenshot               | 133 |

|--------------------------|-----|

| Saving Register Contents | 134 |

| References               | 135 |

| Exercises                | 136 |

4.6 4.7

| Softv | vare En                               | gineering for Embedded Systems              | 139 |

|-------|---------------------------------------|---------------------------------------------|-----|

| 5.1   | Learni                                | 139                                         |     |

| 5.2   | 5.2 Introduction                      |                                             |     |

|       | 5.2.1                                 | Risk Reduction                              | 139 |

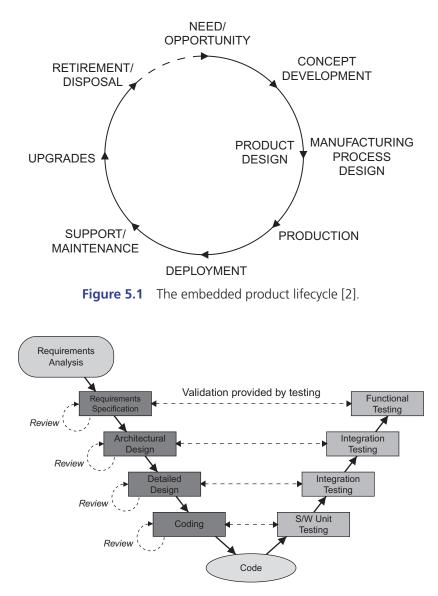

| 5.3   | Softw                                 | are Development Stages                      | 140 |

|       | 5.3.1                                 | Development Lifecycle Overview              | 140 |

|       | 5.3.2                                 | Requirements                                | 143 |

|       | 5.3.3                                 | Design Before Coding                        | 144 |

|       | 5.3.4                                 | Peer Reviews of Design Artifacts            | 145 |

|       | 5.3.5                                 | System Architecture and Design Approach     | 145 |

|       |                                       | Time-Critical Processing                    | 146 |

|       |                                       | Safety-Critical Processing                  | 147 |

|       | 5.3.6                                 | Detailed Design                             | 147 |

|       | 5.3.7                                 | Implementation                              | 149 |

|       | 5.3.8                                 | Software Testing                            | 150 |

|       |                                       | Do We Know How the System is Built?         | 151 |

|       |                                       | How Many Modules Do We Test at a Time?      | 151 |

|       |                                       | How Do We Keep from Breaking Old Bug Fixes? | 152 |

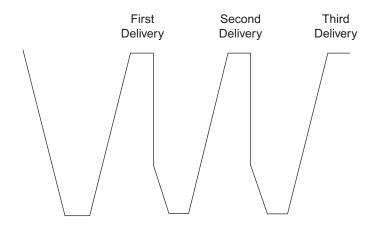

| 5.4   | Software Development Lifecycle Models |                                             | 153 |

|       | 5.4.1                                 | Waterfall Process                           | 153 |

|       | 5.4.2                                 | Iterative Process                           | 154 |

|       | 5.4.3                                 | Spiral Process                              | 154 |

|       | 5.4.4                                 | Agile Development Methods                   | 155 |

|       | 5.4.5                                 | Prototyping                                 | 156 |

| 5.5   | Recap                                 | •                                           | 156 |

| xii | Contents   |     |

|-----|------------|-----|

| 5.6 | References | 156 |

| 5.7 | Exercises  | 157 |

| CHAPTER SIX |          |                                                                             |     |  |  |

|-------------|----------|-----------------------------------------------------------------------------|-----|--|--|

| Conv        | erting E | Between the Analog and Digital Domains                                      | 159 |  |  |

| 6.1         | Learni   | ng Objectives                                                               | 159 |  |  |

| 6.2         | Basic (  | Concepts                                                                    | 159 |  |  |

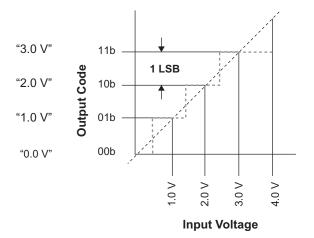

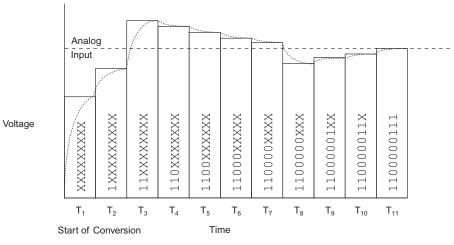

|             | 6.2.1    | Analog to Digital Conversion by Successive Approximation                    | 161 |  |  |

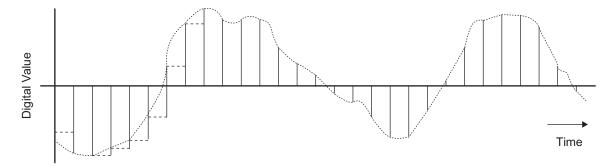

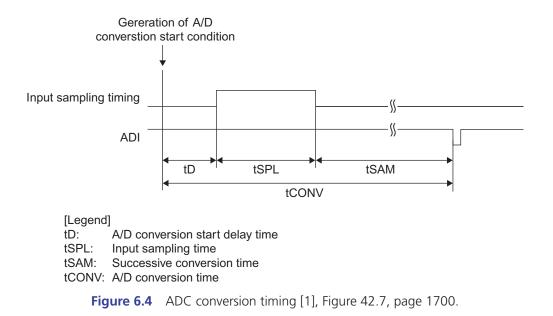

|             | 6.2.2    | Conversion Speed                                                            | 163 |  |  |

|             | 6.2.3    | Transfer Function Calculation                                               | 163 |  |  |

| 6.3         | Basic I  | Examples                                                                    | 165 |  |  |

|             | 6.3.1    | Conversion Speed                                                            | 165 |  |  |

|             | 6.3.2    | Digital Value for a Given Analog Value                                      | 165 |  |  |

|             | 6.3.3    | Step Size                                                                   | 166 |  |  |

| 6.4         | Advar    | nced Concepts                                                               | 166 |  |  |

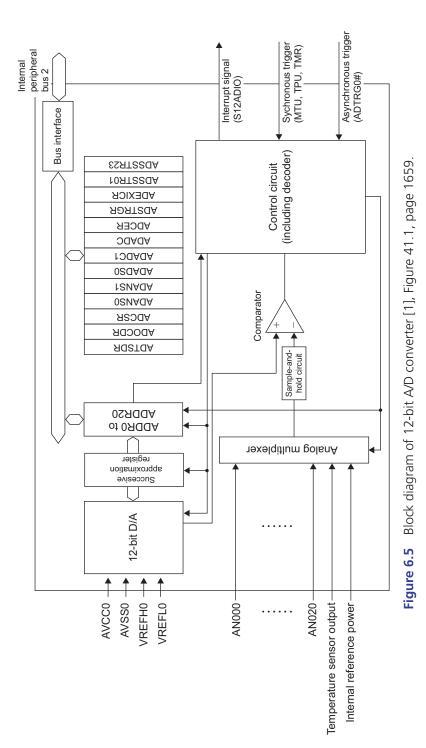

|             | 6.4.1    | 12-Bit A/D Converter                                                        | 166 |  |  |

|             |          | Registers                                                                   | 168 |  |  |

|             |          | A/D Data Registers n (ADDRn) ( $n = 0$ to 20)                               | 168 |  |  |

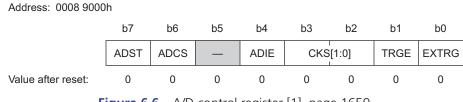

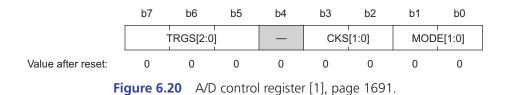

|             |          | AID Control Register (ADCSR)                                                | 168 |  |  |

|             |          | A/D Channel Select Registers (ADANSx ( $x = 0$ or 1))                       | 169 |  |  |

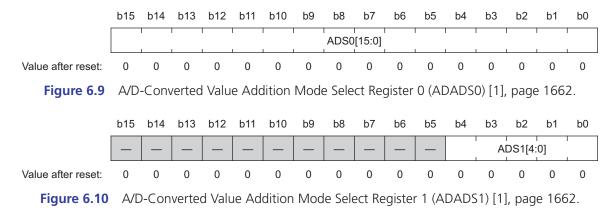

|             |          | A/D-Converted Value Addition Mode Select Registers (ADADSx ( $x = 0$ or 1)) | 170 |  |  |

|             |          | A/D-Converted Value Addition Count Select Register (ADADC)                  | 171 |  |  |

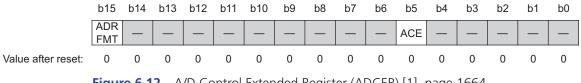

|             |          | AID Control Extended Register (ADCER)                                       | 171 |  |  |

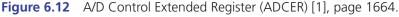

|             |          | AID Start Trigger Select Register (ADSTRGR)                                 | 172 |  |  |

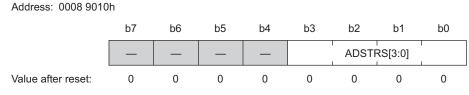

|             |          | A/D-Converted Extended Input Control Register (ADEXICR)                     | 173 |  |  |

|             |          | A/D Temperature Sensor Data Register (ADTSDR)                               | 173 |  |  |

|             |          | A/D Internal Reference Voltage Data Register (ADOCDR)                       | 173 |  |  |

|             |          | Operation                                                                   | 174 |  |  |

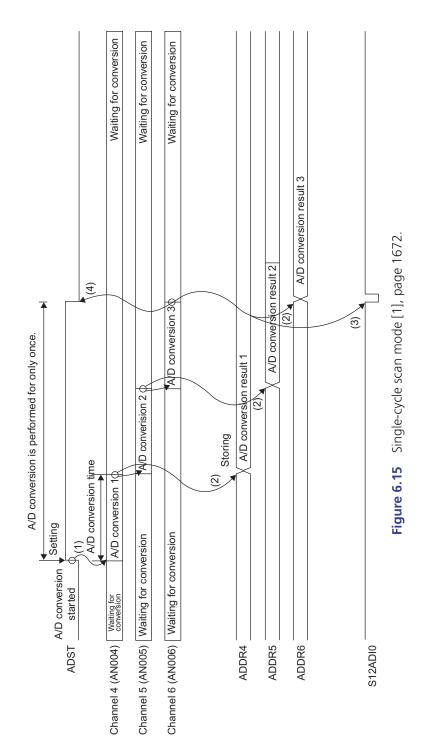

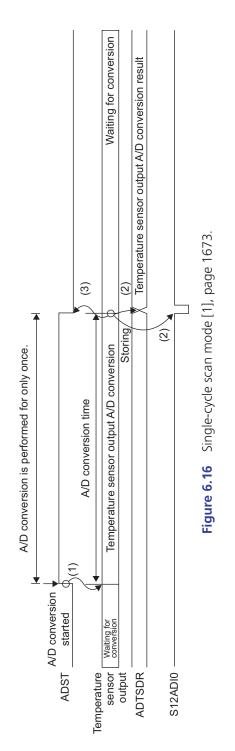

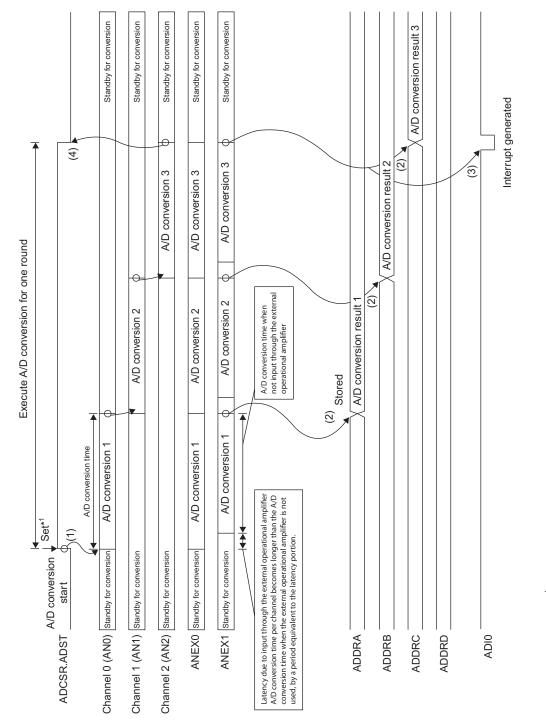

|             |          | Single-Cycle Scan Mode                                                      | 174 |  |  |

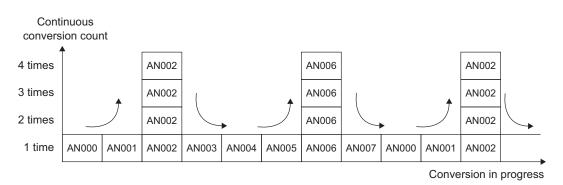

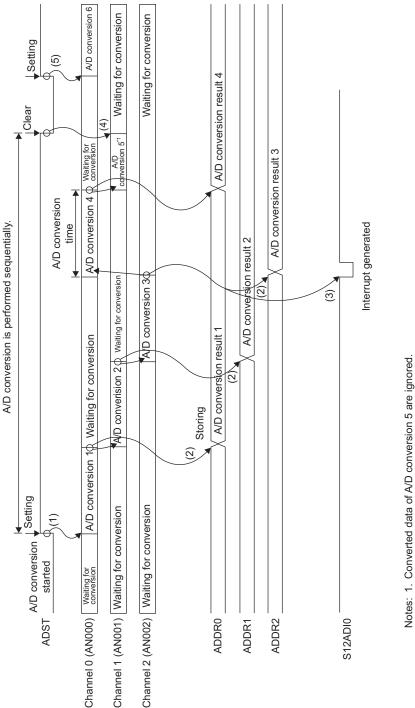

|             |          | Continuous Scan Mode                                                        | 177 |  |  |

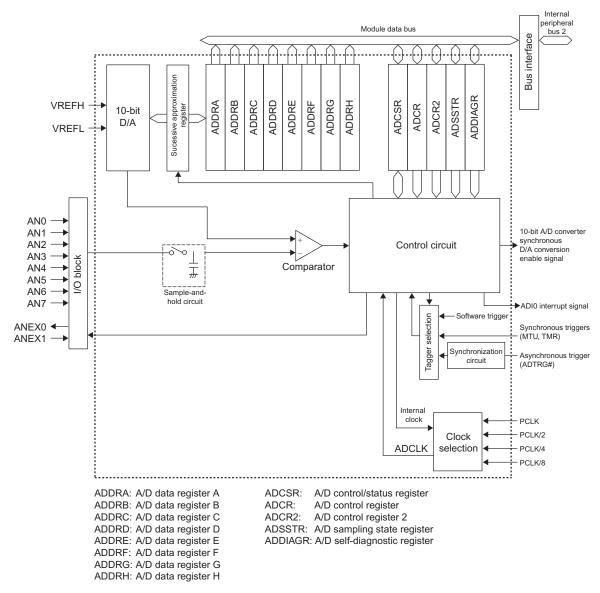

|     | 6.4.2   | 10-Bit ADC                                 | 177 |

|-----|---------|--------------------------------------------|-----|

|     | 0.112   | Registers                                  | 177 |

|     |         | A/D Data Registers (ADDRn) ( $n = A$ to H) | 177 |

|     |         | A/D Control/Status Register (ADCSR)        | 180 |

|     |         |                                            | 180 |

|     |         | A/D Control Register (ADCR)                | 180 |

|     |         | A/D Control Register 2 (ADCR2)             |     |

|     |         | A/D Self-Diagnostic Register (ADDIAGR)     | 182 |

|     |         | Operation                                  | 183 |

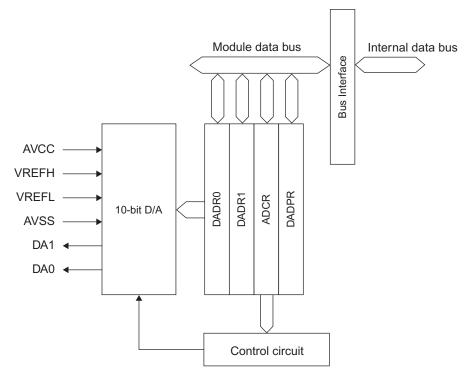

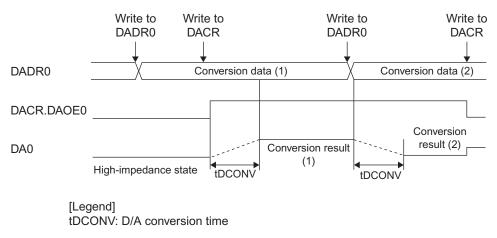

|     | 6.4.3   | D/A Converter                              | 183 |

|     |         | D/A Registers                              | 185 |

|     |         | D/A Data Registers (DADRm) ( $m = 0, 1$ )  | 185 |

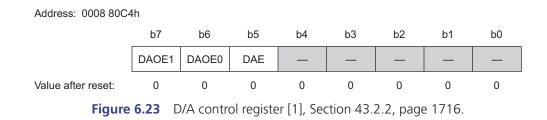

|     |         | D/A Control Register (DACR)                | 185 |

|     |         | DADRm Format Select Register (DADPR)       | 186 |

|     |         | Operation                                  | 187 |

| 6.5 | Advan   | nced Examples                              | 187 |

|     | 6.5.1   | 12-Bit ADC                                 | 187 |

|     |         | Output                                     | 189 |

|     | 6.5.2   | 10-Bit ADC                                 | 189 |

|     |         | Output                                     | 190 |

|     | 6.5.3   | DAC                                        | 191 |

| 6.6 | Recap   |                                            | 191 |

| 6.7 | Refere  | ences                                      | 192 |

| 6.8 | Exercis | ses                                        | 192 |

|     |         |                                            |     |

# **CHAPTER SEVEN**

| Serial | Communications                                                   | 193 |  |

|--------|------------------------------------------------------------------|-----|--|

| 7.1    | Learning Objectives                                              | 193 |  |

| 7.2    | 7.2 Basic Concepts of Serial Communications                      |     |  |

|        | Terminologies                                                    | 194 |  |

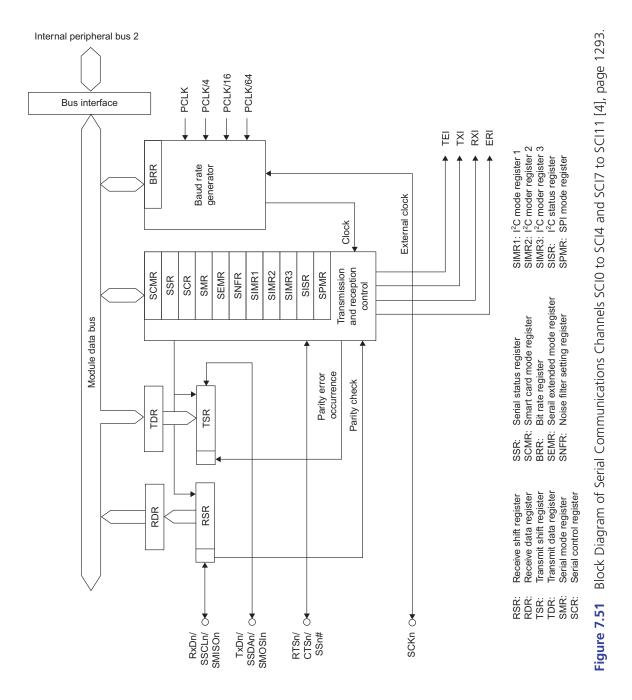

|        | 7.2.1 Introduction to the RX63N Serial Communication Interfacing | 196 |  |

**CONTENTS**

|     | 7.2.2   | Universal Asynchronous Receiver and Transmitter                                 | 198 |

|-----|---------|---------------------------------------------------------------------------------|-----|

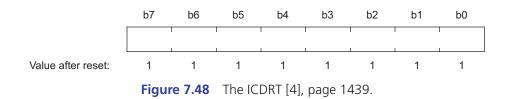

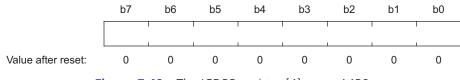

|     |         | Registers Related to the SCI in UART Mode                                       | 200 |

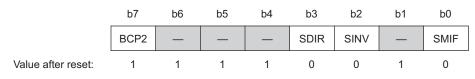

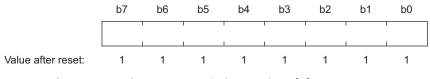

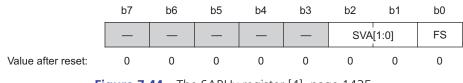

|     |         | Serial Mode Register (SMR)                                                      | 201 |

|     |         | Serial Control Register (SCR)                                                   | 202 |

|     |         | Serial Status Register (SSR)                                                    | 203 |

|     |         | Bit Rate Register (BRR)                                                         | 204 |

|     |         | Transmit Data Register (TDR)                                                    | 205 |

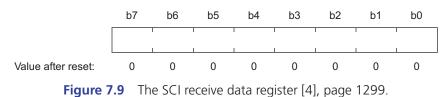

|     |         | Receive Data Register (RDR)                                                     | 205 |

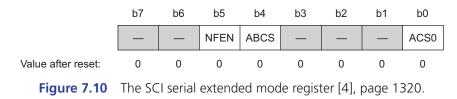

|     |         | Serial Extended Mode Register (SEMR)                                            | 205 |

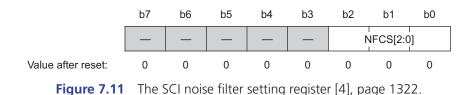

|     |         | Noise Filter Setting Register (SNFR)                                            | 206 |

|     |         | Variations to the UART                                                          | 206 |

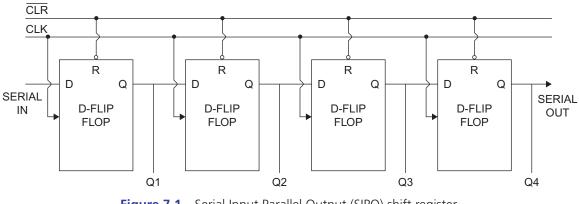

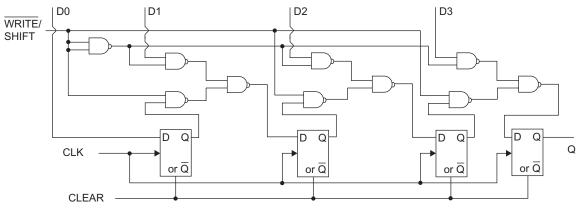

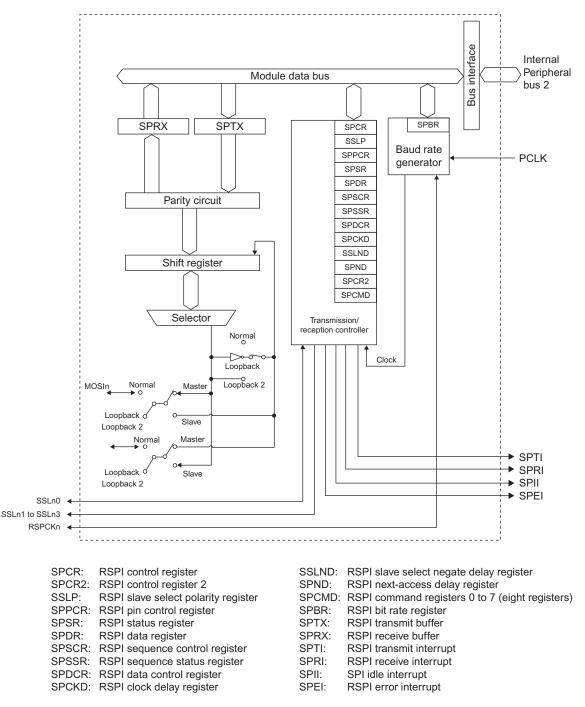

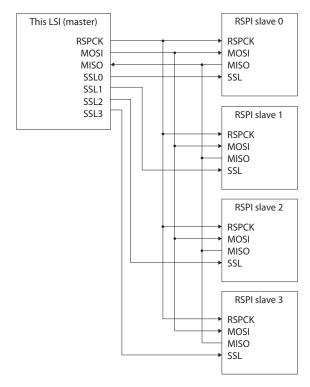

|     | 7.2.3   | Renesas Serial Peripheral Interface                                             | 206 |

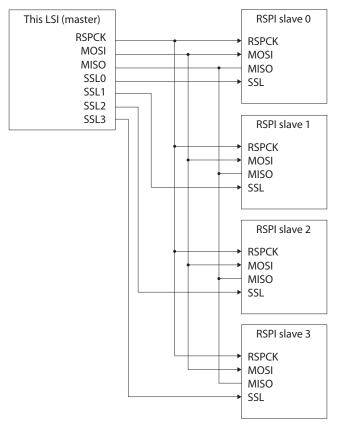

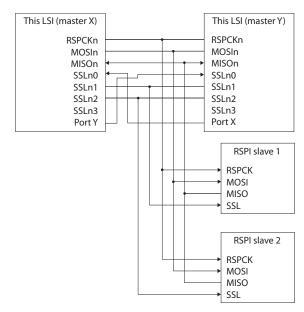

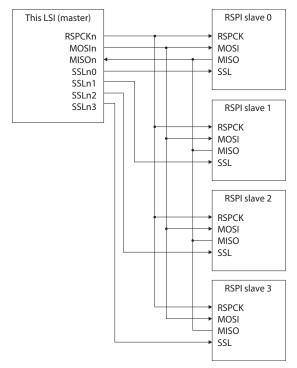

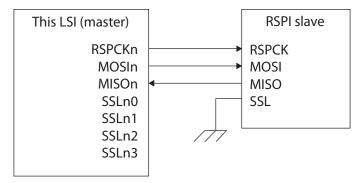

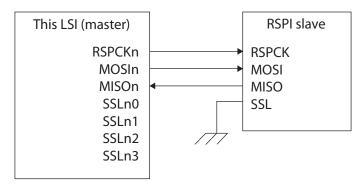

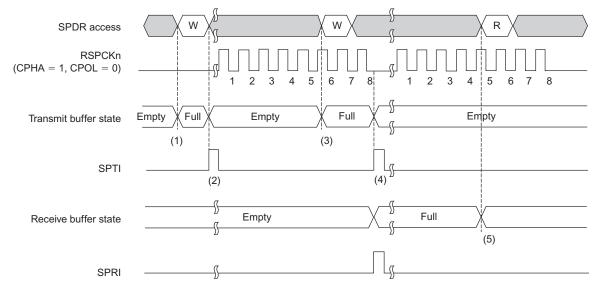

|     |         | General Working of SPI Modules                                                  | 208 |

|     |         | Configurations of the Renesas SPI                                               | 209 |

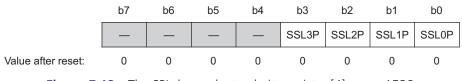

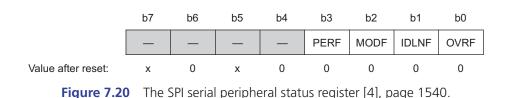

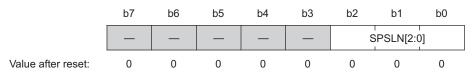

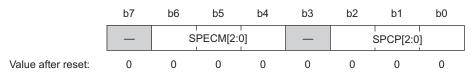

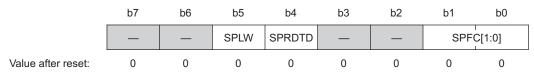

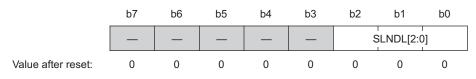

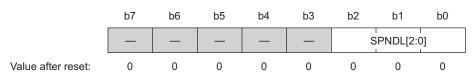

|     |         | Registers Related to the Renesas Serial Peripheral Interface                    | 209 |

|     |         | Configuring the RSPI to Function in Single Master Single Slave Mode             | 220 |

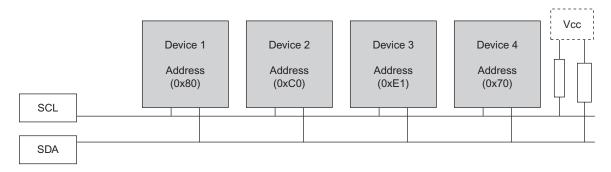

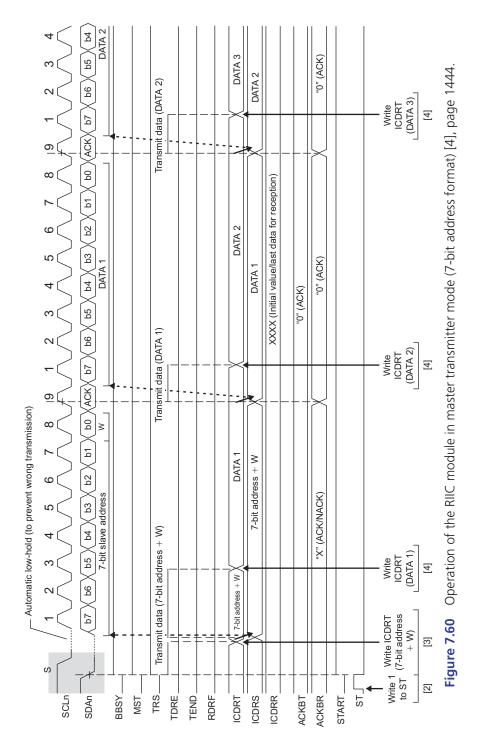

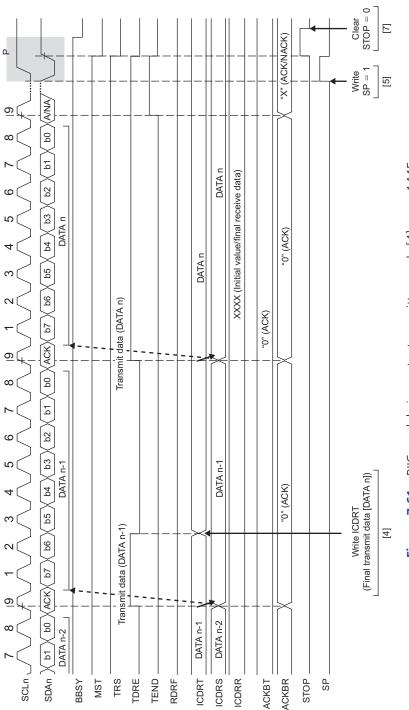

|     | 7.2.4   | Renesas Inter Integrated Circuit Bus                                            | 220 |

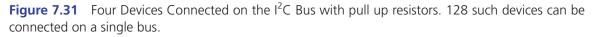

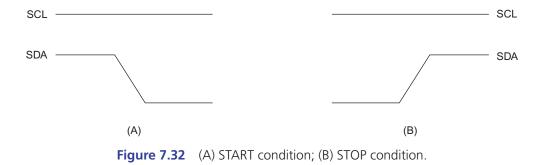

|     |         | I <sup>2</sup> C Bus Protocol                                                   | 221 |

|     |         | I <sup>2</sup> C Communication Modes                                            | 222 |

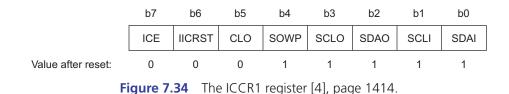

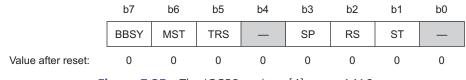

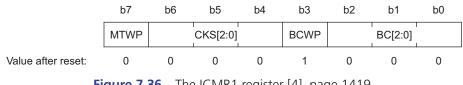

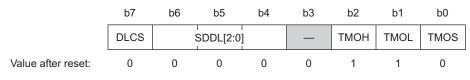

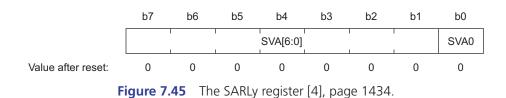

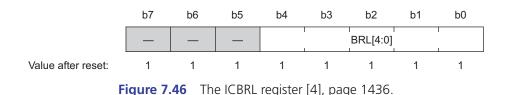

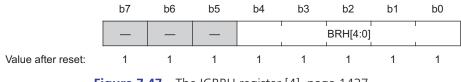

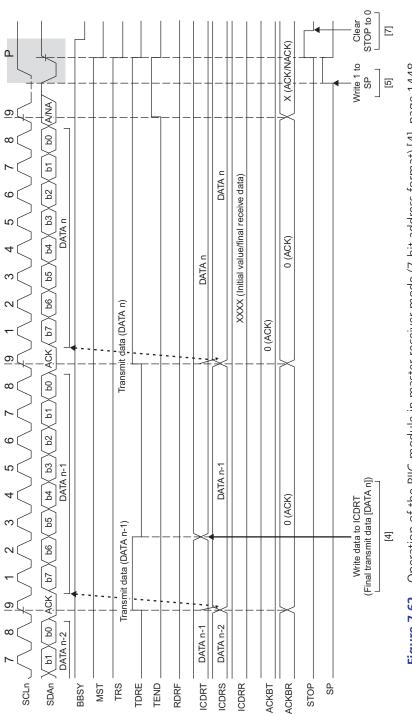

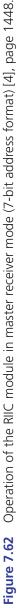

|     |         | Registers related to the RIIC interface                                         | 224 |

| 7.3 | Basic I | Examples                                                                        | 236 |

|     | 7.3.1   | Basic Transmission/Receiving of Serial Data via UART                            | 236 |

|     |         | Explanation of Initialization Code                                              | 239 |

|     |         | Explanation of Transmission Code                                                | 240 |

|     |         | Explanation of Reception Code                                                   | 241 |

|     |         | Explanation of Main Program                                                     | 241 |

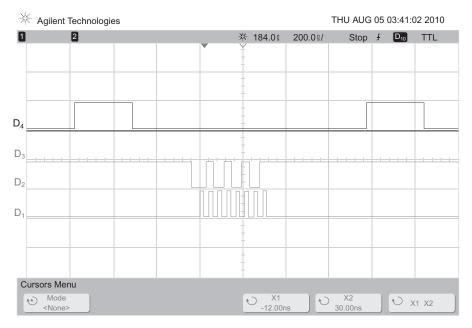

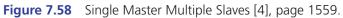

|     | 7.3.2   | Basic Transmission of Data Using Serial Peripheral Interface Bus                | 242 |

|     |         | Explanation of Initialization Code                                              | 244 |

|     |         | Transmission Code                                                               | 245 |

|     |         | Explanation of Transmission Code                                                | 246 |

|     |         | Main Code                                                                       | 246 |

|     |         | Explanation of Main Code                                                        | 246 |

|     | 7.3.3   | Basic Transmission and Reception of Data Using the Renesas I <sup>2</sup> C Bus | 247 |

#### xiv

| 7.4 | Advanced Concepts |                                                                                                     |                 |  |

|-----|-------------------|-----------------------------------------------------------------------------------------------------|-----------------|--|

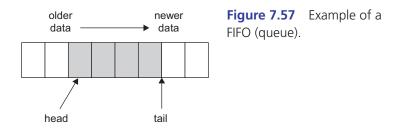

|     | 7.4.1             | Applying FIFO Data Structures for Transmission and Reception Using the UAR Communications Interface | T Serial<br>260 |  |

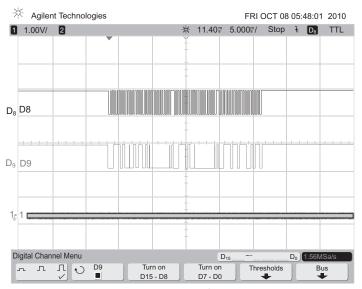

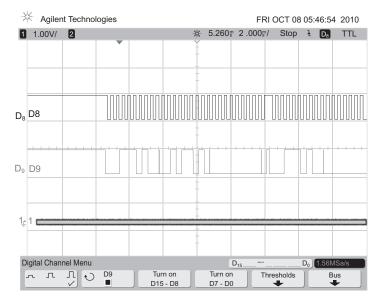

|     | 7.4.2             | Multi-processor Communication Using the Renesas Serial Peripheral Interface                         | 262             |  |

|     |                   | Master Algorithm                                                                                    | 264             |  |

|     |                   | Slave Algorithm                                                                                     | 265             |  |

|     | 7.4.3             | Transfer of Data Between Peripherals Connected on the $I^2C$ Bus Using FIFOs                        | 266             |  |

| 7.5 | Advan             | ced Examples                                                                                        | 274             |  |

|     | 7.5.1             | FIFO Data Structures for Transmission and Reception Using the UART Serial                           |                 |  |

|     |                   | Communications Interface                                                                            | 274             |  |

|     |                   | Setting up Interrupt Service Routines                                                               | 274             |  |

|     |                   | Main Program                                                                                        | 277             |  |

|     | 7.5.2             | Multi-processor Communication Using Queues and the Renesas                                          |                 |  |

|     |                   | Serial Peripheral Interface                                                                         | 278             |  |

|     |                   | Setting Up Interrupt Service Routines                                                               | 278             |  |

|     |                   | Setting Up Function Definitions for Operating on the Queues                                         | 279             |  |

|     |                   | Setting Up All the Function Details Related to the Functioning of the UART                          | and             |  |

|     |                   | FIFO Queues                                                                                         | 280             |  |

|     |                   | Main Program                                                                                        | 283             |  |

|     | 7.5.3             | Transfer of data between peripherals connected on the $I^2C$ bus using FIFOs                        | 284             |  |

| 7.6 | Recap             |                                                                                                     | 295             |  |

| 7.7 | Refere            | nces                                                                                                | 296             |  |

| 7.8 | Exercis           | es                                                                                                  | 296             |  |

# **CHAPTER EIGHT**

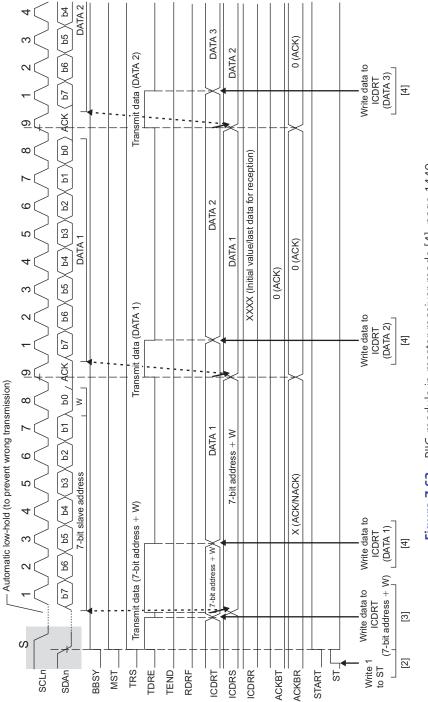

| vent Counters, Timers, and the Real Time Clock |                         | 299                                                                                                            |

|------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|

| Learni                                         | ing Objectives          | 299                                                                                                            |

| Basic Concepts                                 |                         | 299                                                                                                            |

| 8.2.1                                          | Timer and Event Counter | 299                                                                                                            |

|                                                | Timer                   | 299                                                                                                            |

|                                                | Event Counter           | 300                                                                                                            |

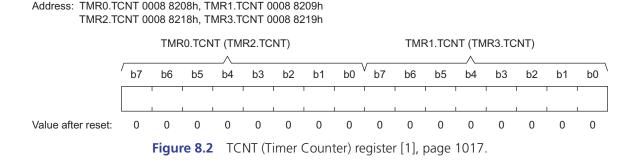

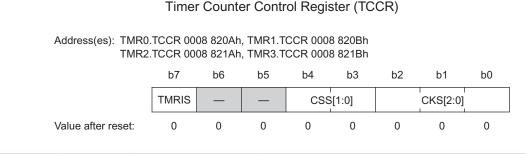

|                                                | Registers               | 303                                                                                                            |

|                                                | Learn<br>Basic          | Learning Objectives<br>Basic Concepts<br>8.2.1 Timer and Event Counter<br><i>Timer</i><br><i>Event Counter</i> |

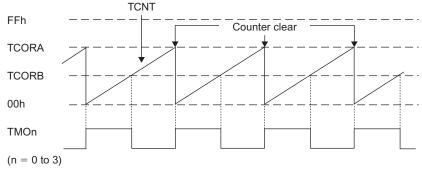

|     | 8.2.2    | Cascading Timers                                                                                                  | 308 |

|-----|----------|-------------------------------------------------------------------------------------------------------------------|-----|

|     | 8.2.3    | Pulse Output Operation                                                                                            | 309 |

| 8.3 | Real Ti  | me Clock                                                                                                          | 311 |

|     | 8.3.1    | RTC Registers                                                                                                     | 312 |

|     | 8.3.2    | Setting the RTC                                                                                                   | 321 |

|     | 8.3.3    | Reading the RTC                                                                                                   | 322 |

|     |          | 16-bit Timer Pulse Unit (TPU)                                                                                     | 323 |

|     |          | TPU Registers                                                                                                     | 324 |

|     |          | Timer Mode Register (TMDR)                                                                                        | 324 |

|     |          | Timer Counter (TCNT)                                                                                              | 326 |

|     |          | Timer General Register (TGRx) ( $x = A$ to D)                                                                     | 326 |

| 8.4 | Basic E  | xamples                                                                                                           | 331 |

|     | 8.4.1    | Setting Up Cascaded Timers                                                                                        | 332 |

|     | 8.4.2    | Setting Up a Timer for Pulse Output                                                                               | 335 |

|     | 8.4.3    | Setting and Reading from the Real Time Clock                                                                      | 336 |

| 8.5 | Advand   | ced Concepts                                                                                                      | 340 |

|     | 8.5.1    | Using a Cascaded Timer with 16-Bit Time Constant Registers                                                        | 340 |

|     | 8.5.2    | Calculating and Programming Pulse Frequency and Duty Cycle in Pulse Output<br>Mode, and Controlling a Servo Motor | 341 |

|     | 8.5.3    | Using the Real Time Clock's Alarm and Periodic Interrupts                                                         | 343 |

| 8.6 | Advand   | ced Examples                                                                                                      | 344 |

|     | 8.6.1    | Using a Cascaded Timer with 16-Bit Time Constant Registers                                                        | 345 |

|     | 8.6.2    | Setting Up Pulse Output Mode to Control a Servo Motor                                                             | 347 |

|     | 8.6.3    | Using the Real Time Clock's Alarm and Periodic Interrupts                                                         | 350 |

| 8.7 | Recap    |                                                                                                                   | 353 |

| 8.8 | Referer  | nces                                                                                                              | 354 |

| 8.9 | Exercise | es                                                                                                                | 354 |

# **CHAPTER NINE**

| Using | nterrupts with Peripherals 3                                  | 55 |

|-------|---------------------------------------------------------------|----|

| 9.1   | Learning Objectives 3                                         | 55 |

| 9.2   | Basic Concepts 3                                              | 55 |

|       | <b>9.2.1</b> Using Interrupts for Tasks versus Other Methods3 | 55 |

| 9.3 | Interru      | ints                                                             | 356 |  |

|-----|--------------|------------------------------------------------------------------|-----|--|

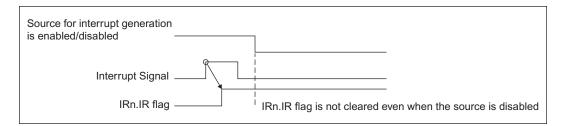

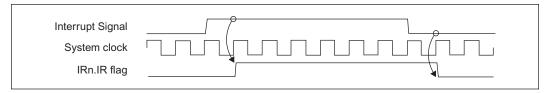

|     |              | Interrupt Request Register n (IRn) (n = interrupt vector number) | 357 |  |

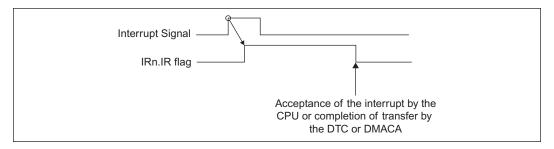

|     |              | IR Flag (Interrupt Status Flag)                                  | 360 |  |

|     |              | Interrupt Priority Register m (IPRm) ( $m = 000$ to 253)         | 361 |  |

|     |              | Fast Interrupt Register (FIR)                                    | 362 |  |

|     |              | Software Interrupt Activation Register (SWINTR)                  | 362 |  |

|     |              | IRQ Control Register i (IRQCRi) ( $i = 0$ to 15)                 | 363 |  |

|     |              | Non-Maskable Interrupt Enable Register (NMIER)                   | 363 |  |

|     |              | Non-Maskable Interrupt Status Register (NMISR)                   | 365 |  |

|     |              | Non-Maskable Interrupt Clear Register (NMICLR)                   | 366 |  |

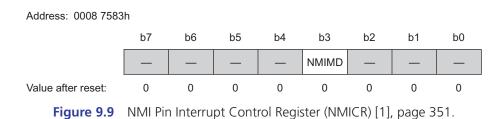

|     |              | NMI Pin Interrupt Control Register (NMICR)                       | 366 |  |

|     | 9.3.1        | Interrupt Vector Table                                           | 367 |  |

|     | 9.3.2        | Interrupt Operation                                              | 367 |  |

|     |              | Edge Detection                                                   | 367 |  |

|     |              | Level Detection                                                  | 368 |  |

|     | 9.3.3        | Setting Up an Interrupt for a Peripheral                         | 369 |  |

|     |              | Setting Up an Interrupt                                          | 369 |  |

|     |              | Registers Set in the ICU for an Interrupt                        | 370 |  |

|     | 9.3.4        | How an Interrupt Operates                                        | 373 |  |

| 9.4 | Basic I      | Examples                                                         | 374 |  |

| 511 | 9.4.1        | Polling a Switch for Input versus Using an Interrupt             | 374 |  |

|     | 9.4.2        | Setting up the ADC with an Interrupt                             | 378 |  |

| 9.5 |              | nced Concepts                                                    | 381 |  |

| 5.5 | <b>9.5.1</b> | Minimizing the Amount of Code in Interrupts                      | 381 |  |

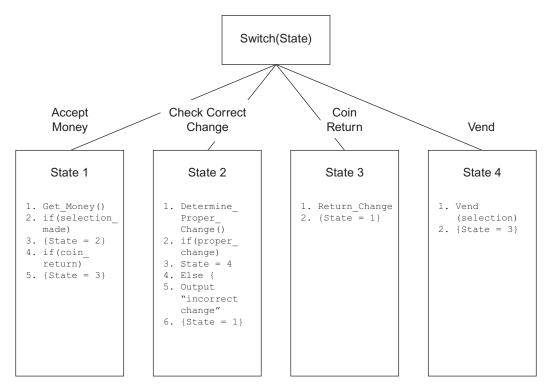

|     | 9.5.2        | Brief Introduction to State Machines                             | 382 |  |

|     | 9.5.3        | State Machines and Using Them with Interrupts                    | 382 |  |

| 9.6 | Advar        | nced Examples                                                    | 384 |  |

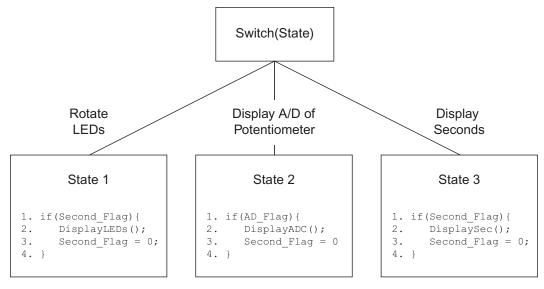

|     | 9.6.1        | Using an ADC Interrupt with Flags to Process Data                | 384 |  |

|     | 9.6.2        | A Simple State Machine Controlled by Interrupts                  | 387 |  |

| 9.7 | Recap        |                                                                  | 393 |  |

| 9.8 | Refere       |                                                                  | 393 |  |

| 9.9 |              |                                                                  | 393 |  |

| 9.9 | 9 Exercises  |                                                                  |     |  |

# **CHAPTER TEN**

| Desig | ning Re | esponsive and Real-Time Systems          | 395 |

|-------|---------|------------------------------------------|-----|

| 10.1  | Learnii | ng Objectives                            | 395 |

| 10.2  | Motiva  | ation                                    | 395 |

| 10.3  | Schedu  | uling Fundamentals                       | 397 |

|       |         | Task Ordering                            | 397 |

|       | 10.3.2  | Task Preemption                          | 399 |

|       | 10.3.3  | Fairness and Prioritization              | 400 |

|       | 10.3.4  | Response Time and Preemption             | 401 |

|       | 10.3.5  | Stack Memory Requirements                | 402 |

|       | 10.3.6  | Interrupts                               | 403 |

| 10.4  | Task IV | lanagement                               | 404 |

|       | 10.4.1  | Task States                              | 404 |

|       | 10.4.2  | Transitions between States               | 405 |

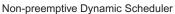

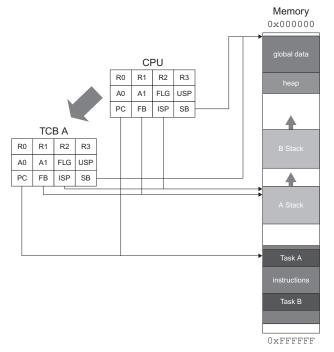

|       | 10.4.3  | Context Switching for Preemptive Systems | 406 |

| 10.5  | Sharin  | g Data Safely                            | 408 |

|       | 10.5.1  | Data Shared Objects                      | 408 |

|       | 10.5.2  | Function Reentrancy                      | 409 |

|       | 10.5.3  | High-Level Languages and Atomicity       | 410 |

|       | 10.5.4  | Shared-Data Solutions and Protection     | 412 |

|       |         | Disable Interrupts                       | 412 |

|       |         | Use a Lock                               | 413 |

|       |         | RTOS-Provided Semaphore                  | 414 |

|       |         | RTOS-Provided Messages                   | 415 |

|       |         | Disable Task Switching                   | 415 |

| 10.6  | Nonpre  | eemptive Dynamic Scheduler               | 415 |

|       | 10.6.1  | Concepts                                 | 415 |

|       | 10.6.2  | Implementation                           | 418 |

|       |         | Task Table                               | 418 |

|       |         | Managing Tasks                           | 419 |

|      | Tick Timer Configuration and ISR               | 421 |

|------|------------------------------------------------|-----|

|      | Scheduler                                      | 422 |

|      | 10.6.3 Example Application using RTC Scheduler | 422 |

| 10.7 | References                                     | 423 |

| 10.8 | Exercises                                      |     |

|      | Appendix                                       | 427 |

|      | Index                                          | 437 |

# **Introduction to Embedded Systems**

# 1.1 LEARNING OBJECTIVES

In this chapter the reader will learn:

- What an embedded system is

- Why to embed a computer

- What functions and attributes embedded systems need to provide

- What constraints embedded systems have

# 1.2 CONCEPTS

An embedded system is an application-specific computer system which is built into a larger system or device. Using a computer system rather than other control methods (such as non-programmable logic circuits, electro-mechanical controls, and hydraulic control) offers many benefits such as sophisticated control, precise timing, low unit cost, low development cost, high flexibility, small size, and low weight. These basic characteristics can be used to improve the overall system or device in various ways:

- Improved performance

- More functions and features

- Reduced cost

- Increased dependability

Because of these benefits, billions of microcontrollers are sold each year to create embedded systems for a wide range of products.

#### 1.2.1 Economics and Microcontrollers

Microcontrollers are remarkably inexpensive yet offer tremendous performance. The microprocessor for a personal computer may cost \$100 or more, while microcontrollers typically cost far less, starting at under \$0.25. Why is this so?

Microcontrollers provide extremely inexpensive processing because they can leverage **economies of scale.** MCUs are programmable in software, so a chipmaker can design a single type of MCU which will satisfy the needs of many customers (when combined with their application-specific software). This reduces the per-chip cost by amortizing the design costs over many millions of units.

The cost of an integrated circuit (such as a microcontroller or a microprocessor) depends on two factors: non-recurring engineering (NRE) cost and recurring cost. The NRE cost includes paying engineers to design the integrated circuit (IC) and verify through simulation and prototyping that it will work properly. The recurring cost is incurred by making each additional IC, and includes raw materials, processing, testing, and packaging.

The IC's area is the major factor determining this recurring cost. The smaller the IC, the more will fit onto a silicon wafer and the lower the recurring cost. Microcontrollers are much smaller than microprocessors for personal computers, so they will cost less (given the same number of ICs sold). The NRE cost must be divided across each IC sold. As the number of ICs sold rises, the NRE adder falls, and so each IC's price falls as well. Low-volume chips are more expensive than high-volume chips.

#### 1.2.2 Embedded Networks

Some embedded systems consist of **multiple embedded computers** communicating across an **embedded network**, and offer further benefits. Each computer on the network uses a communication protocol to share the same set of wires to communicate, rather than dedicating one set for each possible communication route. Several advantages come from having fewer wires:

- Lower parts cost, as fewer wires are needed

- Lower labor costs, as it is faster to assemble

- Greater reliability, as it has fewer connections to fail

Other advantages come from allowing separate nodes to share information. New features may be possible, or the system efficiency may be improved through better coordination of activities among different nodes.

#### 1.3 TYPICAL BENEFITS OF EMBEDDED SYSTEMS \_

As an example, let's examine how embedded systems have affected automobiles. A typical modern car has dozens of microcontrollers embedded within it. Let's see why.

#### 1.3.1 Greater Performance and Efficiency

Computer control of automobile engines lowers pollution and increases fuel efficiency, reducing operating costs.

Burning gasoline with air in spark ignition engines is a tricky business if we want to maximize efficiency, yet minimize pollution. The main factor affecting emissions is the ratio of air mass to fuel mass. The ideal ratio is 14.7 to 1, and the catalytic converter is designed to operate most efficiently at this ratio. If there is too little air (a rich mix), then excessive carbon monoxide (CO) and hydrocarbons (HC) will be produced. If there is too much air (a lean mix), then large amounts of oxides of nitrogen (called NO<sub>x</sub>) will be created. So we would like for each fuel injector to add just the right amount of fuel. This depends on the mass of the air inside the cylinder, which depends on factors such as air temperature and air pressure. These in turn depend on altitude and weather, as well as whether the engine is warmed up or not.

Another factor is the timing of the sparkplug firing. If it fires early, then there is more time for combustion within the cylinder before the exhaust valve opens. This raises the average temperature within the cylinder and changes the combustion process, affecting CO, HC, and  $NO_x$  concentrations.

It would be quite impractical to design a mechanical control system to consider all of these factors and squirt the fuel injectors at just the right instant for the right amount of time. Thankfully, an inexpensive microcontroller is quite effective at these kinds of calculations and control.

#### 1.3.2 Lower Costs

There are various ways in which an embedded system can reduce the costs associated with a device.

- Component costs: Embedded software can compensate for poor signal quality, allowing the use of less-expensive components. For example, a low-cost pressure sensor may be very temperature-dependent. If ambient temperature information is already available, then it is a simple matter to compensate for the temperature-induced error.

- Manufacturing costs: Many vehicles use the Control Area Network (CAN) protocol to communicate across an in-car network. The embedded network reduces assembly and parts costs because of the simpler wiring harness.

- Operating costs: As mentioned above, an embedded system enables automobile engines to operate more efficiently, reducing the amount of gasoline needed and hence lowering operating costs.

- Maintenance costs: Some vehicles predict oil life by monitoring engine use history, notifying the driver when an oil change is needed.

3

#### 4 EMBEDDED SYSTEMS USING THE RENESAS RX63N MICROCONTROLLER

#### 1.3.3 More Features

An MCU running application-specific software offers tremendous opportunities for features and customization. These features can make your company's products stand out from the competition.

- **Cruise control** keeps the car running at the same speed regardless of hills, wind, and other external factors.

- Smart airbags reduce injuries by adjusting inflation speed based on passenger weight.

- **Power seats** move to each driver's preferred position automatically, based on whose keyless entry fob was used to open the car.

- Headlights and interior lights shut off automatically after a time delay if the car is not running and prevents the lights from draining the battery.

### 1.3.4 Better Dependability

Embedded systems and networks offer many opportunities to improve dependability.

- An engine controller (and other controllers) can provide various "limp-home modes" to keep the car running even if one or more sensors or other devices fail.

- A warning of an impending failure can be provided.

- Diagnostic information can be provided to the driver or service personnel, saving valuable trouble-shooting time.

# 1.4 EMBEDDED SYSTEM FUNCTIONS

There are several common functions which embedded systems typically provide.

- **Control systems** monitor a process and adjust an output variable to keep the process running at the desired set point. For example, a cruise control system may increase the throttle setting if the car's speed is lower than the desired speed, and reduce it if the car is too fast.

- There is often sequencing among multiple states. For example, a car engine goes through multiple states or control modes when started. During Crank and Start, the fuel/air mix is rich and depends on the engine coolant temperature. Once the engine has started, the controller switches to the Warm-Up mode, in order to raise the engine and exhaust system temperatures to their ideal levels. Here the fuel/air

mixture and ignition timing are adjusted, again based in part on the engine coolant temperature. When the engine has warmed up it can switch into **Idle** mode. In this mode the controller seeks to minimize the engine's speed, yet still run smoothly and efficiently despite changes in loads due to air conditioning, power steering, and the electrical system.

- Signal processing modifies input signals to eliminate noise, emphasize signal components of interest, and compensate for other factors. For example, a hands-free speakerphone interface may use multiple microphones, beam-forming, and active noise cancellation to filter out low-frequency road noise. Other sensors may have spark-plug noise filtered out.

- **Communications and networking** enable different devices on the same network to exchange information. For example, the engine controller may need to send a message indicating speed. To do this, the speed value must be formatted according to the communication protocol and then loaded into the network interface peripheral for transmission.

### 1.5 ATTRIBUTES OF EMBEDDED SYSTEMS \_

Embedded systems are designed so that the resulting device behaves in certain desirable ways.

- Embedded systems need to respond to events which occur in the environment, whether a user presses a button or a motor overheats. A system which is not sufficiently responsive is not likely to be a successful product. For example, when we press a channel select button for the radio, we would like for it to respond within some reasonable time.

- For real-time systems, the timing of the responses is critical because late answers are wrong answers. Igniting the fuel in a cylinder is time-critical because bad timing can damage or destroy engine components (to say nothing of reducing power, or the efficiency and pollution concerns mentioned previously).

- Embedded systems typically require sophisticated fault handling and diagnostics to enable safe and reliable operation. Often the fault handling code is larger and more complex than the normal operation code. It is easy to design for the "everything goes right and works fine" case. It is far more difficult to determine methods to handle the exceptional cases. What is likely to fail? Which failures can lead to dangerous conditions? How should the system handle failures? How will you test that the system handles the failures correctly?

- Embedded systems may be expected to operate independently for years without operator attention such as adjustment or resetting. The system is expected to

5

operate robustly and always work. Given that it is very difficult and expensive to write perfect, bug-free software, developers build in mechanisms to detect faulty behavior and respond, perhaps by restarting the system.

# 1.6 CONSTRAINTS ON EMBEDDED SYSTEMS \_

Embedded systems often have **constraints** which limit the designer's options, and can lead to creative and elegant solutions. These constraints are typically different from those for general-purpose computers.

- Cost is a common constraint. Many applications which use embedded systems are sold in very competitive markets, in which price is a major factor. Often a manufacturer will hire subcontractors to design and build individual sub-systems. This allows the manufacturer to pit potential subcontractors against each other, keeping prices down.

- There may be size and weight limits for portable and mobile applications. An embedded system for an automotive remote keyless entry transmitter must fit into a small fob on a key ring which fits easily into a pocket. Similarly, the receiver must not be too heavy. A heavier car will have worse acceleration, braking, cornering, and fuel efficiency. Aircraft and spacecraft are especially sensitive to weight since a heavier craft requires more fuel to achieve the same range.

- There may be limited **power** or **energy** available. For example, a battery has a limited amount of energy, while a solar cell generates a limited amount of power. High temperatures may limit the amount of cooling available, which will limit the power which can be used.

- The **environment** may be harsh. Automotive electronics under the hood of a car need to operate across a wide range of temperatures (-40°C to 125°C, or -40°F to 193°F), while withstanding vibrations, physical impact, and corroding salt spray. Spark plugs generate broadband radio frequency energy which can interfere with electronics.

# 1.7 DESIGNING AND MANUFACTURING EMBEDDED SYSTEMS

Embedded systems are designed with a central microcontroller and other supporting electronic components mounted on a printed circuit board (PCB). PCBs provide the means to connect these integrated circuits to each other to make an operational system. The PCB provides structural support and the wiring of the circuit. The individual wires on the PCB are called traces and are made from a flat copper foil. While many circuit designs may use the same standard components, the PCB is often a custom component for a given design.

7

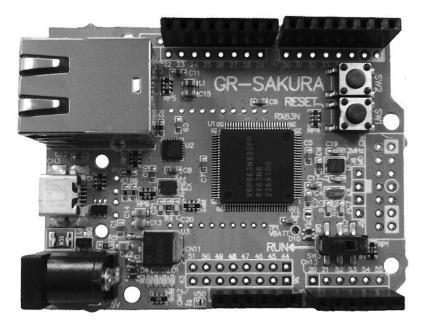

Figure 1.1 Renesas Sakura Board.

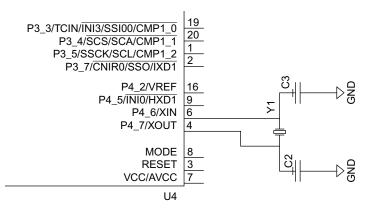

Designing a PCB requires a completed schematic for the circuit. This schematic is sometimes different than the schematic seen in textbooks. It often contains extra information about the components and construction of the board. For example, a textbook schematic may only show a battery for the power supply, while the production schematic would show the battery case, the number of cells, the rating of the battery, and the manufacturers of the components.

From the schematic, a designer will use their computer-aided design tools to identify the size of the PCB, and then place the electronic components on their board drawing. The designer will also place the wiring between the components on the PCB.

The physical PCB is manufactured from a fiberglass-resin material that is lightweight and inexpensive. A manufacturer will add copper wiring traces to the surfaces of the board and the appropriate insulation and white silk screening. The final manufacturing steps are applying solder, placing the components, and heating/cooling the solder. Figure 1.1 shows an example of a finished board.

The completed boards are electrically tested for functionality. Any board failing the test is inspected in more detail to find the problems. These boards are repaired to increase the passing rate acceptable to the manufacturer. The boards are wrapped in antistatic materials and shipped to the next location for the next stage of production, or immediately installed in a mechanical enclosure (like the mechanical shell of a mobile phone).

#### 1.8 AN EXAMPLE OF AN EMBEDDED SYSTEM: THE RENESAS SAKURA BOARD \_\_\_\_\_

The Renesas Sakura Board (Figure 1.1) is one example of a Renesas MCU-based embedded system. This device has fifty-five digital I/O lines that are controlled by the Renesas microcontroller. [1]

Some of the main components to note are the 100/10 Mbps Ethernet port in the upper left, a micro USB port right beneath the Ethernet port which is used to program the built-in flash memory, and at the bottom left a 5 V DC power jack. The Sakura also has a micro SD card slot located on the underside of the board.

The large chip in the center is a Renesas R5F563NBDDFP microcontroller from the RX Family of chips with 1024 K of flash memory, 128 Kbytes of RAM, and 32 Kbytes of data flash. Fifty-five I/O pins are used to interface with external pins on the module. This processor runs at 96 MHz [2].

#### 1.9 SUMMARY OF BOOK CONTENTS \_

This book is structured as follows:

- Chapters 2 and 3 present basic microcontroller concepts and the specifics of the RX63N.

- Chapters 4 and 5 show how software is built. At the low level they show how programs are compiled and downloaded. At the high level they show software engineering concepts and practices.

- Chapters 6 through 8 present how to use peripherals to interface with the environment and simplify programs.

- Chapter 9 presents how to use interrupts to improve response times and program structure.

- Chapter 10 presents how to structure multi-threaded software so the resulting system is predictably responsive.

### 1.10 RECAP \_\_\_\_\_

An embedded system is an application-specific computer system which is built into a larger system or device. Using a computer system enables improved performance, more functions and features, lower cost, and greater dependability. With embedded computer systems, manufacturers can add sophisticated control and monitoring to devices and other systems, while leveraging the low-cost microcontrollers running custom software.

9

# 1.11 REFERENCES \_\_\_\_\_

- [1] Renesas. Gadget Renesas. Renesas Electronics America, Inc. 2013. Web. Accessed at http://www.renesas. com/products/promotion/gr/index.jsp#board

- [2] Renesas Electronics, Inc., *RX63N Group, RX631 Group User's Manual: Hardware, Rev.1.60*, February 2013.

# **Concepts of Microcontrollers**

# 2.1 LEARNING OBJECTIVES

Embedded systems consist of computers embedded in larger systems. Additional circuitry such as power supplies, clock generators, and reset circuits, is required for the computer to work. Transducers (devices that convert one type of energy into another) are also used to connect microcontrollers to the outside world. There are two classes of transducers: inputs and outputs. Inputs are also known as "sensors" and contain such things as switches, keypads, and buttons. Output transducers include devices such as LEDs, motors, and coils.

In this chapter the reader will learn general information about:

- Connecting LEDs

- Connecting motors and coils

- Connecting switches and buttons

- Connecting keypads

- Analog to digital conversion

- Digital to analog conversion

- Power supplies for embedded systems

- Clock generation options

- Reset circuitry

# 2.2 INTERFACING WITH DIGITAL SIGNALS

#### 2.2.1 General Purpose Digital I/O

Embedded systems consist of computers embedded in larger systems. The processor needs to sense the state of the larger system and environment, and control output devices. The most basic way to do this is through one or more discrete signals, each of which can be in one of two states (on or off). General purpose digital I/O **ports** are the hardware which can be used to read from or write to the system outside the microcontroller.

The RX63N has eighteen I/O ports (Port 0 to 9, A to G, J). Each port has eight pins, except for ports 0 and F which have 6 pins, and port J which has 2 pins, and on most ports all pins can be selected as inputs or outputs. However, on some ports some pins are reserved. The reserved pins cannot be configured as I/O pins. Each port has a Port Direction Register (PDR), Port Output Data Register (PODR), Port Input Register (PIDR), Open Drain Control Registers (ODRy, y = 0, 1), Pull-up Resistor Control Register (PCR), Drive Capacity Control Register (DSCR), and Port Mode Register (PMR). The pins of a port may serve several purposes; for example, Port 4 pin 0 can be used as a general purpose I/O pin, as an A/D converter input, or as an interrupt input. Depending on the purposes these pins serve, they might have extra registers.

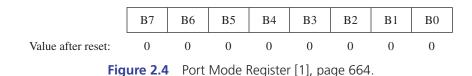

#### Port Direction Register (PDR)

This register, as the name suggests, is used to set the data direction (input or output) of a pin. PDR is a read/write register. Each bit of the Port Direction Register represents a pin.

|                    | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|--------------------|----|----|----|----|----|----|----|----|

| Value after reset: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 2.1 Port Direction Register [1], page 661.

The 'iodefine.h' file has C code constructs that make it easy to access each port with C code. Each port is defined as a *structure* and each register of the port is defined as a *union* of variables within that structure. An example of how the PDR is defined inside a port *structure* follows:

```

1. struct st port4 {

2.

union {

3.

unsigned char BYTE;

4.

struct {

5.

unsigned char B7:1;

6.

unsigned char B6:1;

7.

unsigned char B5:1;

8.

unsigned char B4:1;

9.

unsigned char B3:1;

10.

unsigned char B2:1;

11.

unsigned char B1:1;

12.

unsigned char B0:1;

13.

} BIT;

14.

} PDR;

15. }

```

Line 1 shows that Port 0 has been defined as a *structure*. Lines 2 to 14 suggest that the Port Direction Register (PDR) has been defined as a *union* with the variable BYTE and a structure called BIT. This organization helps in easy access of the bits of the PDR. Unsigned char Bn:1(n = 0 to 7) indicates that the character variable is assigned 1 bit.

To select a particular pin as the input pin, the corresponding bit of the PDR has to be set to '0'; and to select a pin as output, the corresponding bit of the PDR has to be set to '1.' The general syntax to set a bit of the PDR is PORTx.PDR.BIT.Bn (x = 0 to 9, A to G, J; and n = 0 to 7) since ports are defined as *structures* and accessing structure *members* is done so this way. To configure multiple pins at the same time, the *char* variable BYTE can be used. All pins are configured as inputs at reset, by default.

#### **EXAMPLE 1**

#### Set Switch 1 (Port 4 bit 0) as Input

PORT4.PDR.BIT.B1 = 0;

When a pin is selected as an input from a peripheral, the Port Mode Register (PMR) has to be enabled. The PMR will be explained a little later.

Selecting a pin as an output involves setting the Port Output Data Register (PODR) and the Port Direction Register (PDR).

#### Port Output Data Register (PODR)

The Port Output Data Register is used to store data for pins that have been configured as output pins. This register is similar to the PDR in that each bit of the register represents a pin and certain bits of certain ports are reserved.

|                    | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|--------------------|----|----|----|----|----|----|----|----|

| Value after reset: | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 2.2 Port Output Data Register [1], page 662.

The Port Output Data Register (PODR) is also defined as a *union* of variables inside the port *structure*, in the 'iodefine.h' file. It is presented just like the PDR. Unsigned char: 1 is used to represent reserved pins.

The syntax to access the bits of the Port Output Data Register (PODR) is PORTx.PODR.BIT.Bn (x = 0 to 9, A to G, J; and n = 0 to 7). To select a pin as an output pin, first set the Port Output Data Register (PODR) to a known value, preferably 0, so that changes in the output can be easily observed. The *char* variable BYTE can be used to set multiple pins as output at the same time.

#### EXAMPLE 2

#### Set LED1 (Port D bit 0) as Output

- 1. PORTD.PDR.BIT.B0 = 1;

- 2. PORTD.PODR.BIT.B0 = 0;

Line 1 sets LED1 as an output and line 2 switches on the LED.

#### Sets LEDs 1, 2, and 3 (Port D bit 0, 1, and 2) as Outputs

- 1. PORTD.PDR.BYTE =  $0 \times 07$ ;

- 2. PORTD.PODR.BYTE = 0xF8;

Line 1 sets LED1, 2, and 3 as outputs and line 2 switches on the LEDs.

#### Port Input Data Register (PIDR)

Port register is also defined as a *union* of variables inside the port *structure* in the 'iodefine.h' file. PORTx.PIDR.BIT.Bn (x = 0 to 9, A to G, J; and n = 0 to 7) is used to read the state of a pin and the state is stored in the Port Input Register regardless of the value in the Port Mode Register (PMR). This register also has some reserved bits. These bits are read as 1 and cannot be modified.

Figure 2.3 Port Input Data Register.

#### Check State of Switch1 (Port 4 bit 0) and Turn On LED1 (Port D bit 0)

```

1. if(PORT4.PIDR.BIT.B0 == 1){

2.     PORTD.PODR.BIT.B0 = 1;

3. }

```

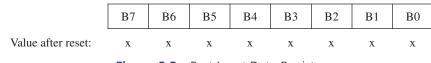

#### Port Mode Register (PMR)

This register is used to buffer the input values for pins that have been configured as input from peripheral modules.

Before configuring a pin as an input from a peripheral, the PMR must be enabled. To enable the PMR set PORTx.PMR.BIT.Bn (x = 0 to 9, A to G, J; and n = 0 to 7) to 1. If a pin has to be configured as an output pin, set PORTx.PMR.BIT.Bn (x = 0 to 9, A to G, J; and n = 0 to 7) to 0. Setting PMR to 0 disables the PMR. While setting the PMR, make sure that the corresponding pin is not in use. For example, when setting IRQi (i = 0 to 15) as input, first disable the interrupts, next enable PMR and then enable interrupts. It is necessary to follow the above steps to avoid unintended operations from taking place.

#### Open Drain Control Registers (ODR0/ODR1)

Most output pins function as CMOS but some output pins can operate as CMOS or NMOS open-drain pins. Since NMOS circuits are faster compared to the CMOS circuits, which consist of the slower p-channel transistors, using NMOS open-drain pins as outputs would be similar to a wired-OR connection. All of the pins of all ports are capable of functioning as NMOS open-drain output pins. Setting PORTx.ODRy.BIT.Bn (x = 0 to 9, A to G, J; and y = 0 or 1: to 1, selects the pin as an NMOS open-drain pin.

#### Pull-Up Resistor Control Register (PCR)

Some devices have limited signal swing. When such a device is interfaced with the RX63N board, the signal from the device has to be pulled up so that it is in the valid voltage range of the board (this is not the typical usage, the typical usage is the external device is only capable of pulling down; or there is nothing attached and you do not want the port to float). To simplify this kind of interfacing, pull-up MOS circuitry is available for all

ports. To enable pull-up MOS for a particular pin of a port, set PORTx.PCR.BIT.Bn (x = 0 to 9, A to G J; and n = 0 to 7) to 1. To disable pull-up MOS, set PORTx.PCR.BIT.Bn (x = 0 to 9, A to G, J; and n = 0 to 7) to 0. The PCR is automatically disabled for pins configured as outputs. To enable or disable pull-up MOS for multiple pins use PORTx.PCR.BYTE command. The value of the PCR after reset is 0x00.

#### Drive Capacity Control Register (DSCR)

This register is used to switch the drive capacity of a port. The default value of 0 sets the pin as normal-drive output. Setting PORTx.DSCR.BIT.B0 (x = 0 to 5, A to E, H and J) or PORTx.DSCR.BIT.Bn (x = 0, 2, 5, 9, A to E, and G; and n = 1 to 7) to 1, selects the pin as high-drive output.

#### 2.2.2 Example 1: Reading Switches to Control LEDs

#### Using LEDs as Outputs

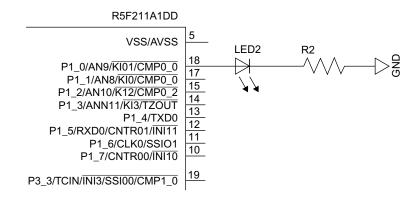

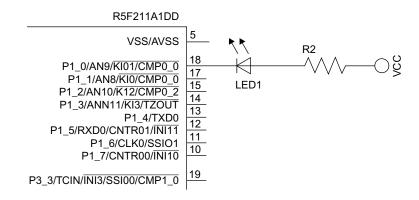

LEDs require a current-limiting resistor so that they do not draw too much current from the I/O pin to which they are connected. Most microcontrollers can sink more current than they can supply, so generally LEDs are connected with the cathode to the microcontroller pin, and a current-limiting resistor between the anode and supply voltage. Formula 2.1 shows how to calculate the value of the current limiting resistor. Figure 2.5 shows the two ways of connecting LEDs to a microprocessor.

$$R = (V_{\text{Output}} - V_{\text{LED}})/I_{\text{LED}}$$

Formula 2.1

**Figure 2.5A** The microprocessor is sourcing current to an LED. Turning on this LED requires a logical high signal on the output pin. If the LED is attached to Port D, Pin O, and that pin is set to an output; then the code needed to turn the LED on would be: PORTD.PDR.BIT.BO = 1;

**Figure 2.5B** The microprocessor is sinking current from the LED. Turning on the LED requires a logical low on the output pin. If the LED is attached to Port D, Pin O, and that pin is set to an output; then the code needed to turn the LED on would be: PORTD.PDR.BIT.BO = 0;

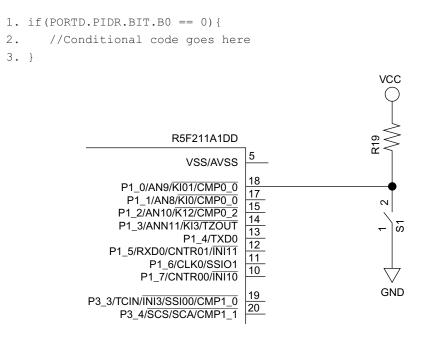

#### Using Switches as Inputs

A simple interfacing design can include using a pull-up resistor on a pin that is also connected to ground through a button or switch. The resistor will pull the voltage on that pin to logical high until the button connects to ground. When the button is pressed, the voltage at that pin will drop to zero (logical low). Figure 2.6 shows a schematic of this approach. If the switch in Figure 2.6 is connected to Port D pin 0, the code to check this switch would be:

Figure 2.6 Basic button connection to a microprocessor input pin.

Contact bounce is a worry with any mechanical switch. When the switch is closed, the mechanical properties of the metals in the switch cause the contacts to literally bounce off of one another. This can cause false signals to be read as inputs. Your design should take this into account with either a hardware or software *debouncing* solution. Hardware debouncing circuits often require digital logic as well as some resistors and capacitors. Hardware debouncing circuits are very useful for interrupt pins. Software debouncing is accomplished by setting up a timer to check the state of the switch at a set interval, such as every 1 ms. If the value of the input has been the same for the duration of the timer (1 ms in this case) the input can be considered valid. This method helps to ignore false input values.

To better understand configuring I/O pins let us look at an example. The RX63N board has three push buttons and twelve LEDs (six red and six green). Switches and LEDs are simple I/Os and in the following program we will see how to set up switches as inputs and LEDs as outputs. According to this program, when switch1 is pressed, green LEDs will glow, when switch2 is pressed, red LEDs will glow, and when switch3 is pressed, all the LEDs will glow.

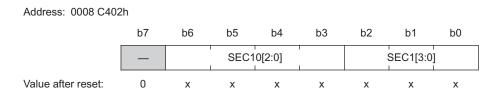

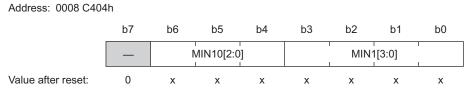

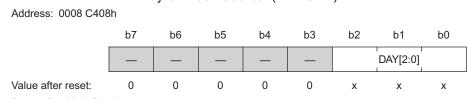

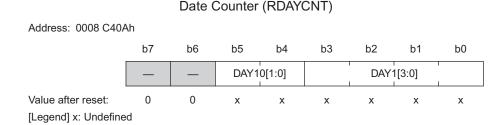

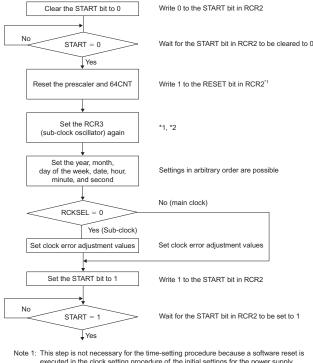

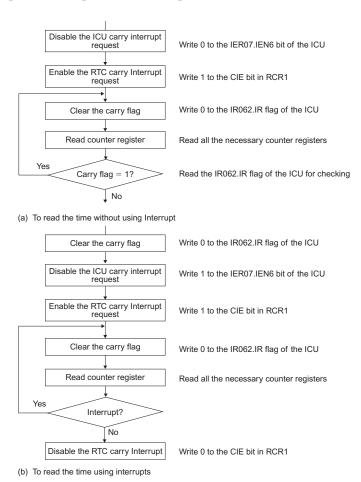

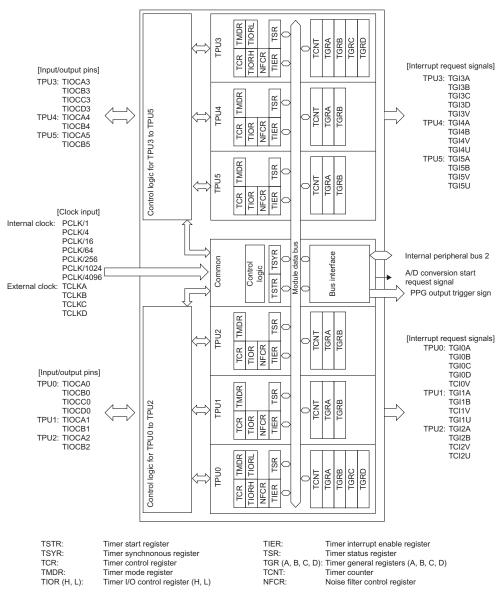

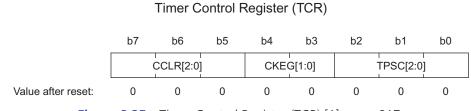

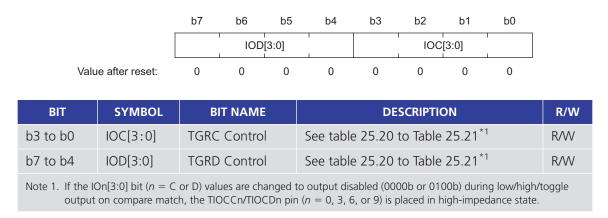

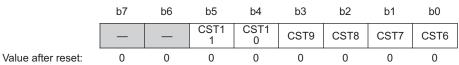

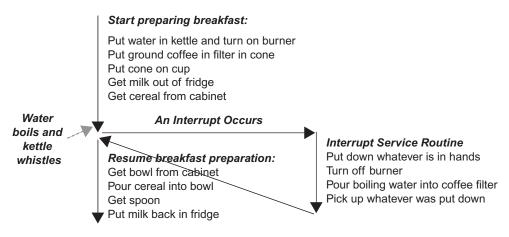

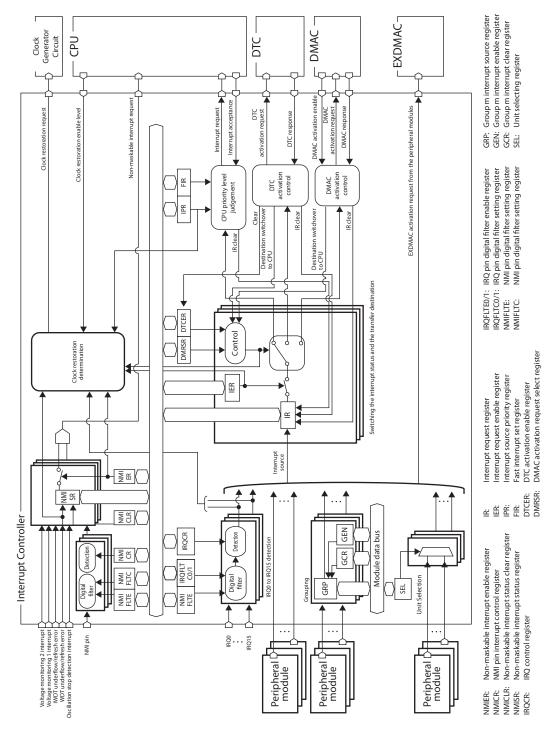

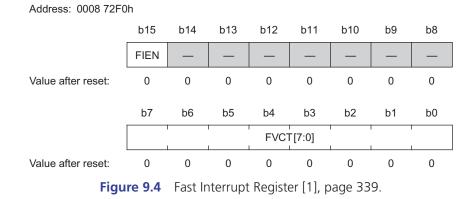

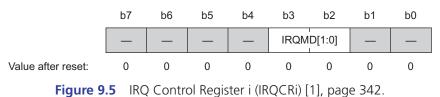

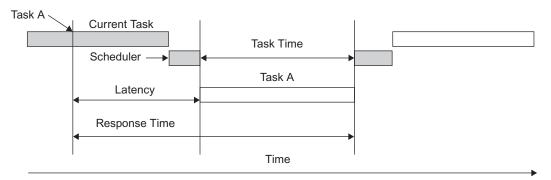

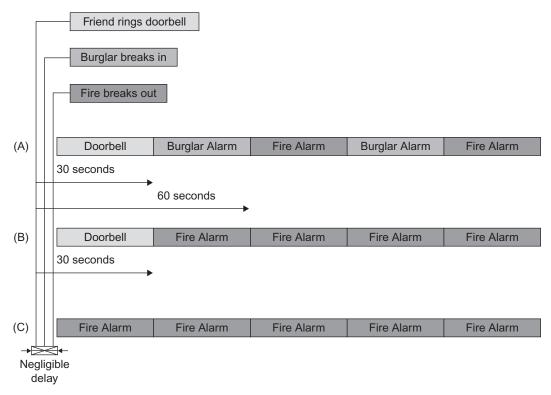

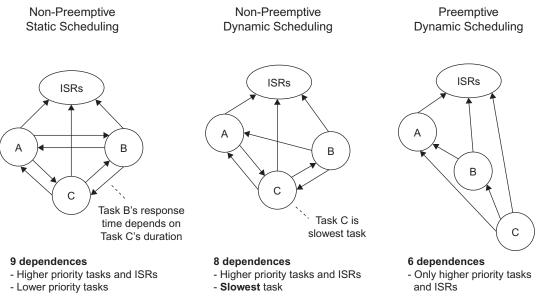

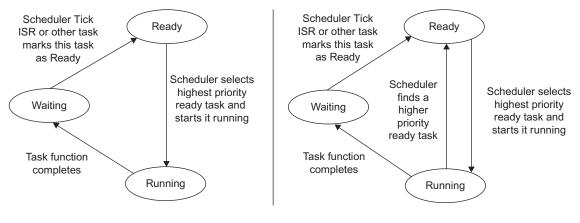

- 1. #include "iodefine.h"