# M16C/62

# Using the M16C/62 DMAC in Forward Source Mode

#### 1.0 Abstract

The following article introduces and shows an example of how to use the DMAC function of the M16C/62 with a forward counting source address and fixed destination address.

#### 2.0 Introduction

The Renesas M16C/62 is a 16-bit MCU based on the M16C CPU core with 256 KB of user Flash. The MCU has two DMAC (Direct Memory Access Controller) channels that allow data to be transferred from a source memory location to a destination memory location without using the CPU. The DMAC utilizes the same internal address and data busses as the CPU yet is given a higher priority to the data bus than the CPU. This method of DMAC and CPU bus arbitration is termed a cycle stealing method.

Each DMAC controller is capable of transferring data to or from a fixed address to any other address in the 1Mbyte address space. The DMAC controllers can automatically transfer 128k bytes of data using word (16-bit) transfers, or 64k bytes of data using byte (8-bit) transfers. The source or destination address can also be auto-incremented. DMAC transfers can be initiated by an interrupt request signal or by manually writing to the software DMA request bit. When requests are initiated by an interrupt request signal, neither the interrupt enable flag (I flag) nor the interrupt priority level affects the DMA transfers.

## 3.0 DMAC with Forward Source, Fixed Destination

In the forward source counting address, fixed destination address mode, the DMAC controller will transfer bytes or words from an incrementing source address (that increments after each transfer) to a fixed destination address. The transfers can be either bytes or words. Loading a value into the transfer count register controls the number of automated transfers. Transfers will continue to occur each time the DMAC trigger event occurs until the transfer register underflows, therefore the number loaded into the register should be 1 less than the number of transfers desired. A control register bit determines whether each transfer is a byte or word of data. When the DMAC controller is configured to perform a single transfer cycle, the DMAC becomes disabled after the transfer register underflows. In the repeat mode the Source Pointer register and the Transfer Counter register are reloaded with their initial values after the Transfer Counter register underflows and the DMAC remains active. Therefore, in the repeat mode, transfers will occur each time a trigger event occurs until the DMA enable bit is set inactive ("0").

# 4.0 Configuring the DMAC for Forward Source, Fixed Destination

To configure a DMAC channel, the following choices must be configured (the configurations for this example are shown in parentheses):

- 1. Select the DMA request cause (UART0 receive interrupt request).

- 2. Select fixed or forward source (forward source).

- 3. Select fixed or forward destination (fixed destination).

- 4. Select 8 or 16-bit transfers (8-bit transfers).

- Select a single transfer or multiple transfers (single transfer).

- 6. Select the source address for the transfer (Buffer address in RAM).

- 7. Select the destination address for the transfer UART0 transmit buffer address).

- 8. Select the number of bytes to be transferred (10).

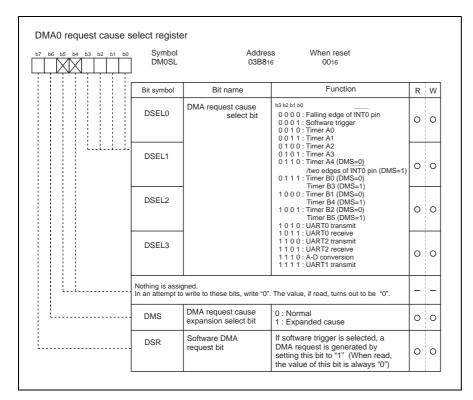

The registers that are used to configure and control the DMAC channels are shown in Figure 1.

Figure 1 DMA0 Request Cause Select Register

| b6 b5 b4 b3 b2 b1 b0 | Symbol<br>DM1SL                                                                                                | Addres<br>03BA1                        |                                                                                                                                              |     |

|----------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                      | Bit symbol                                                                                                     | Bit name                               | Function                                                                                                                                     | R W |

|                      | DSEL0                                                                                                          | DMA request cause select bit           | b3 b2 b1 b0  0 0 0 0 : Falling edge of INT1 pin 0 0 0 1 : Software trigger 0 0 1 0 : Timer A0 0 0 1 1 : Timer A1                             | 0 0 |

|                      | DSEL1                                                                                                          |                                        | 0 1 0 0 : Timer A2<br>0 1 0 1 : Timer A3(DMS=0)<br>/serial I/O3 (DMS=1)<br>0 1 1 0 : Timer A4 (DMS=0)<br>/serial I/O4 (DMS=1)                | 0 0 |

|                      | DSEL2                                                                                                          |                                        | 0 1 1 1 : Timer B0 (DMS=0) /two edges of INT1 (DMS=1) 1 0 0 0 : Timer B1 1 0 0 1 : Timer B2 1 0 1 0 : UART0 transmit 1 0 1 1 : UART0 receive | 0 0 |

|                      | DSEL3                                                                                                          |                                        | 1 1 0 0 : UART2 transmit<br>1 1 0 1 : UART2 receive<br>1 1 1 0 : A-D conversion<br>1 1 1 1 : UART1 receive                                   | 0 0 |

|                      | Nothing is assigned. In an attempt to write to these bits, write "0". The value, if read, turns out to be "0". |                                        |                                                                                                                                              |     |

|                      | DMS                                                                                                            | DMA request cause expansion select bit | 0 : Normal<br>1 : Expanded cause                                                                                                             | 0 0 |

|                      | DSR                                                                                                            | Software DMA request bit               | If software trigger is selected, a DMA request is generated by setting this bit to "1" (When read, the value of this bit is always "0")      | 0 0 |

| b7 b6 b5 b4 b3 b2 b1 b0                 | Symbol<br>DMiCON                                                                                               | Address 002C16, 003C                                                                                              | When reset 00000X002                       |          |               |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------|---------------|

|                                         | Bit symbol                                                                                                     | Bit name                                                                                                          | F unction                                  | R        | W             |

|                                         | DMBIT                                                                                                          | Transfer unit bit select bit                                                                                      | 0 : 16 bits<br>1 : 8 bits                  | 0        | 0             |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | DMASL                                                                                                          | Repeat transfer mode select bit                                                                                   | 0 : Single transfer<br>1 : Repeat transfer | 0        | 0             |

|                                         | DMAS                                                                                                           | DMA request bit (Note 1)                                                                                          | 0 : DMA not requested<br>1 : DMA requested | 0        | O<br>(Note 2) |

| 1                                       | DMAE                                                                                                           | DMA enable bit                                                                                                    | 0 : Disabled<br>1 : Enabled                | 0        | 0             |

| 1 1 1 1                                 | DSD                                                                                                            | Source address direction select bit (Note 3)                                                                      | 0 : Fixed<br>1 : Forward                   | 0        | 0             |

| 1                                       | DAD                                                                                                            | Destination address direction select bit (Note 3)                                                                 | 0 : Fixed<br>1 : Forward                   | 0        | 0             |

| L.I                                     | Nothing is assigned. In an attempt to write to these bits, write "0". The value, if read, turns out to be "0". |                                                                                                                   |                                            | -        | -             |

|                                         | Note 2: This bi<br>Note 3: Source                                                                              | equest can be cleared by rest can only be set to "0".  address direction select bit be set to "1" simultaneously. | and destination address direction s        | select b | oit           |

**Figure 2 DMA Control Registers**

**REU05B0010-0100Z June 2003** Page 3 of 6

#### 5.0 Reference

**Renesas Technology Corporation Semiconductor Home Page**

http://www.renesas.com

#### E-mail Support

support apl@renesas.com

#### **Data Sheets**

• M16C/62 datasheets, 62aeds.pdf

#### 6.0 Software Code

The example program was written to run on the MSV1632 Starter Kit but could be modified to implement in a user application. The program is written in C (the NC30 Compiler). The program demonstrates using the DMA0 channel to transfer data from a memory buffer to the UART0 transmit buffer. The program performs a single transfer of 10 bytes to UART0. At the completion of the transfer a DMA0 interrupt request is generated. UART0 on the starter kit board is connected to a 9-pin DB connector that can be used to connect to a PC running a terminal program, such as HyperTerminal. With the program running, the data contained in the DATA array will be sent to the terminal program and appear on the PC screen.

```

/*****************************

main

Parameters: None

None

Returns:

Description: Initializes the system and then loops forever.

*********************

void main()

ptr string= &data[0];

uart init ();

// initialize UARTO and pre-load first character

// in transmit buffer

DMA init ();

// initialize DMA registers

// enable DMA transfers

dmae_dm0con = 1;

asm ("fset I");

// enable interrupts

// enable UARTO transmit

te u0c1 = 1;

while (1);

//loop forever

}

/*****************************

DMA init

None

Parameters:

None

Description: Initializes DMA for transfer from forward source to fixed

destinations. Sets DMACO for 10 byte transfers from memory to UARTO

transmit buffer

void DMA init(void)

dm0sl = 0x0a; /* DMA0 trigger select UART0 transmit

00001010;

|||||||||-----(DSEL0) the four bits (DSEL3-DSEL0) the DMA

|||||||-----(DSEL1) request cause set for UARTO transmit

||||||||-----(DESEL2)

|||||||----(DSEL3)

||||----not used set to 0

|||----not used set to 0

||----(DMS) DMA request cause expansion bit to normal

|-----(DSR) set to 1 to generate DMA request if software

trigger selected */

dm0con = 0X11;

/* DMAO single transfer, 8 bit mode, forward source,

fixed destination /*

00010001;

||||||||-----(DMBIT) transfer unit bit select bit 1 = 8 bits

|||||||-----(DMASL) repeat transfer mode 0 = single transfer

||||||----(DMAS) DMA request bit can only be set to 0

|||||-----(DMAE) DMA enable bit 0= disabled

| | | | | ----- (DSD) source address direction 1 = forward

```

```

|||-----(DAD) destination address direction 0 = fixed

||-----not used set to 0

|----not used set to 0 */

dar0 = (unsigned long) \&u0tb; // set destination register to address

// of uart0 transmit buffer

sar0 = (unsigned long)ptr string; // set source register to address of

// beginning of data buffer

tcr0 = 0x9;

// set transfer counter for 10 transfers

// (number of transfers -1)

dm0ic = 0x04;

// set interrupt priority for DMA0

// interrupt to 4

}

dma0 isr

Parameters: None

None

Returns:

Description: This service routine is entered after the completion of the DMA

transfer

********************

void dma0 isr(void)

}

/*****************************

uart init

Parameters: None

None

Returns:

Description: Initializes uart

void uart init(void)

int dummy;

// Configure Uart0 for 9600 baud, 8 data bits, 1 stop bit, no parity

u0mr = 0x05;

// set mode register

u0c0 = 0x10;

// set control register

u0brg = 0x67;

// set bit rate generator

// (16Mhz/16/9600)-1

u0tb = 0x20;

// Place data in the transmit buffer

// so when the transmit enable bit is set

// later on, this first byte will be sent

// out and cause a UART transmit interrupt

// to occurs triggering the DMAC

s0tic = 0x00;

// Disable UARTO receive interrupt,

}

```

### Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

## Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and

algorithms represents information on products at the time of publication of these materials, and are

subject to change by Renesas Technology Corporation without notice due to product improvements

or other reasons. It is therefore recommended that customers contact Renesas Technology

Corporation or an authorized Renesas Technology Corporation product distributor for the latest

product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Renesas Technology Corporation semiconductors are not designed or manufactured for use in a

device or system that is used under circumstances in which human life is potentially at stake. Please

contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product

distributor when considering the use of a product contained herein for any specific purposes, such as

apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea

repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be

exported under a license from the Japanese government and cannot be imported into a country other

than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.