# Mitsubishi M16C Instruction Set Architecture

Lecture 2

# Today

Learn about Mitsubishi (Renesas) processor

- Lecture covers ISA, derived from Assembler

Language Programming Manual

(M16C\_Assembler.pdf MALPM Ch. 1, 2)

- Registers: General Purpose, Control

- Instruction Set

- Addressing Modes

- Memory Map

# **Software Manual** (M16C\_Software\_Manual.pdf): pp.1-32

Use chapter 3 as a reference. You are responsible for this material – not memorizing it, but instead being able to figure out what an instruction does, or finding an instruction to do something

# **Data Sheet**

(M16C62\_Hardware\_Manual\_rev1.20.pdf)

– pp. 1-27

$k \ge m$  array of stored bits (k is usually  $2^n$ ) Address

- unique (n-bit) identifier of location

#### Contents

- m-bit value stored in location

#### **Basic Operations:**

## LOAD

- read a value from a memory location

# STORE

- write a value to a memory location

| 0000 |          |

|------|----------|

| 0001 |          |

| 0010 |          |

| 0011 | 00101101 |

| 0100 |          |

| 0101 |          |

| 0110 |          |

|      | •        |

| 1101 | 10100010 |

| 1110 |          |

| 1111 |          |

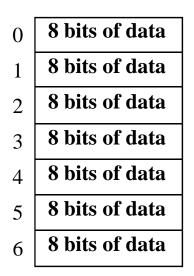

# **Simple Memory Organization**

Viewed as a large, single-dimensional array A memory address is an index into the array "Byte addressing" means that the index points to a byte of memory

• • •

# **Memory Organization**

Bytes are nice, but most data items use larger "words"

- For M30626, a word is 16 bits or 2 bytes.

$2^{16}$  bytes with byte addresses from 0, 1, 2 to  $2^{16}$ -1  $2^{15}$  words with byte addresses 0, 2, 4, ...  $2^{16}$ -2

. . .

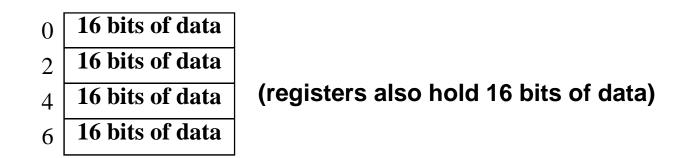

# Endianness

Big endian: most significant byte is stored at the lowest byte address

- Ex: 68000, PowerPC, Sun SPARC

- <u>Little endian</u>: least significant byte is stored at the lowest address

- Ex: x86, DEC VAX, Alpha

- Most of the time we will avoid this issue in class by only loading/storing words or loading/storing bytes

- If two processors with different conventions use a local area network, a disk drive, etc., YOU need to pay attention to endianness

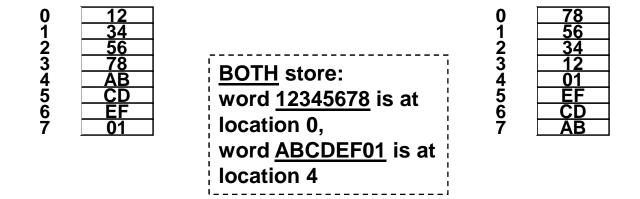

# **Big Endian-What does it look like?**

#### Imagine you have the following hexadecimal values:

- 0x11 22 33 44

- 0x55 66 77 88

- Oxaa bb cc dd

- 0xEE FF 00 99

- 0x01 23 45 67 . . . .

And we put them in memory, starting at memory address 0x10000000. What would it look like?

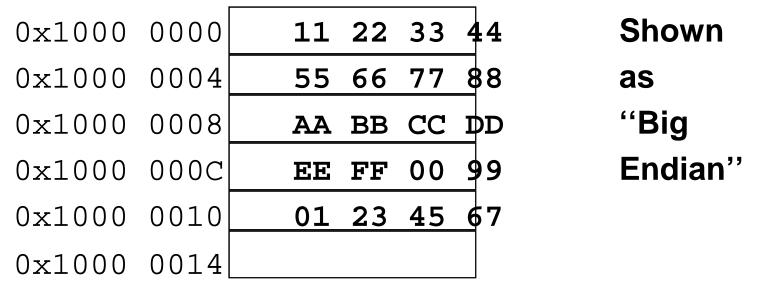

# Little Endian -What does it look like?

#### Imagine you have the following hexadecimal values:

- 0x11 22 33 44

- 0x55 66 77 88

- 0xAA BB CC DD

- 0xEE FF 00 99

- 0x01 23 45 67

#### And we put them in memory, starting at memory address 0x10000000. What would it look like?

| 33 22 11 Sh        | 44 33 22 11 | Shown    |

|--------------------|-------------|----------|

| 77 66 55 as        | 88 77 66 55 | as       |

| <u>сс вв аа</u> "L | DD CC BB AA | "Little  |

| <u>00 FF EE</u> Er | 99 00 FF EE | Endian'' |

| 45 23 01           | 67 45 23 01 |          |

|                    |             |          |

| 11 22 33 4 | Ox1000 0000 | 0x1000          |

|------------|-------------|-----------------|

| 55 66 77 8 | Ox1000 0004 | 0x1000          |

| AA BB CC I | Ox1000 0008 | 0x1000          |

| EE FF 00 9 | Ox1000 000C | 0x1000          |

| 01 23 45 6 | Ox1000 0010 | $0 \times 1000$ |

| 0x1000 | 0000 |

|--------|------|

| 0x1000 | 0004 |

| 0x1000 | 0008 |

| 0x1000 | 000C |

| 0x1000 | 0010 |

| 44 | 33 | 22 | 11 |

|----|----|----|----|

| 88 | 77 | 66 | 55 |

| DD | CC | BB | AA |

| 99 | 00 | FF | EE |

| 67 | 45 | 23 | 01 |

Shown as ''Little Endian''

# Data Formats for the M30626

Ν

N+1

N+3

#### Byte

- 8 bits

- signed & unsigned

- .B suffix for instruction

## Word

- 16 bits

- signed & unsigned N+2

- .W suffix

# Address &

longword

Limited to specific instructions

| b7   | b0 |

|------|----|

| DATA |    |

|      |    |

|      |    |

|      |    |

|      |    |

Byte (8-bit) data

|     | b7  | b0   |

|-----|-----|------|

| N   | DAT | A(L) |

| N+1 | DAT | A(M) |

| N+2 | DAT | A(H) |

| N+3 |     |      |

|     |     |      |

20-bit (Address) data

# Is the M30626 big or little endian?

Ν

N+1

N+2

N+3

Ν

N+1

N+2

N+3

| b7 |        | b0 |

|----|--------|----|

|    | DATA(L | )  |

|    | DATA(H | )  |

|    |        |    |

|    |        |    |

|    |        |    |

Word (16-bit) data

| b7      | b0 |

|---------|----|

| DATA(LL | .) |

| DATA(LH | I) |

| DATA(HL | .) |

| DATA(HH | ł) |

|         |    |

Long Word (32-bit) data

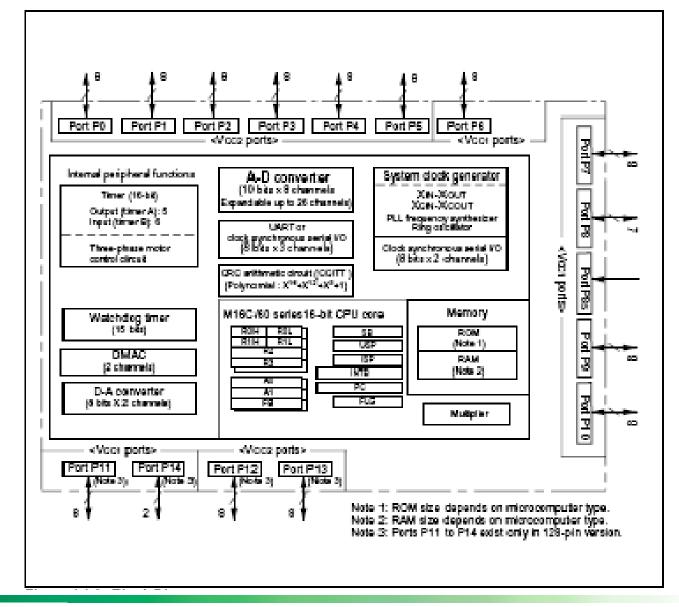

# **Review of the M30626 Architecture**

Microcontroller has:

- General Purpose

Registers

- RAM

- Flash

- EEPROM

- Digital Ports

- Analog Ports

- Timers

- Oscillator

- DMA Controller

- Reliability and safety

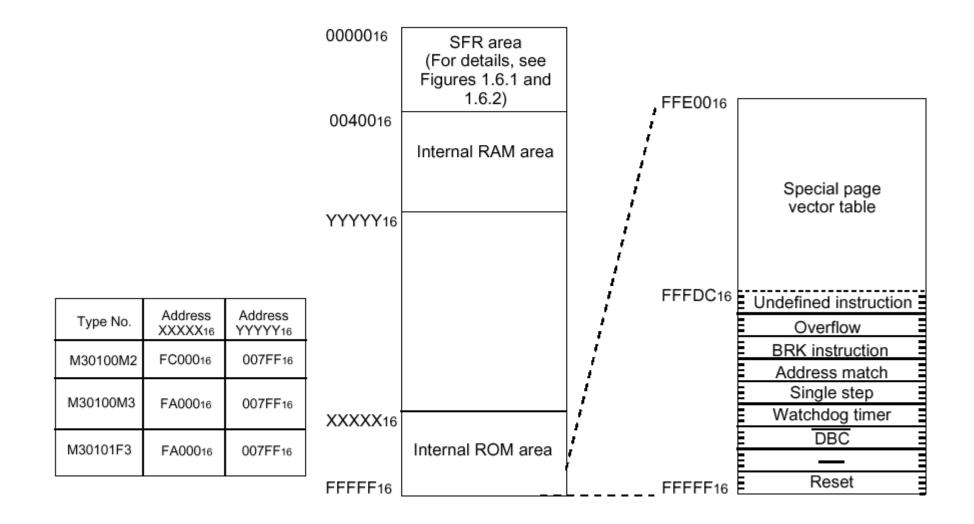

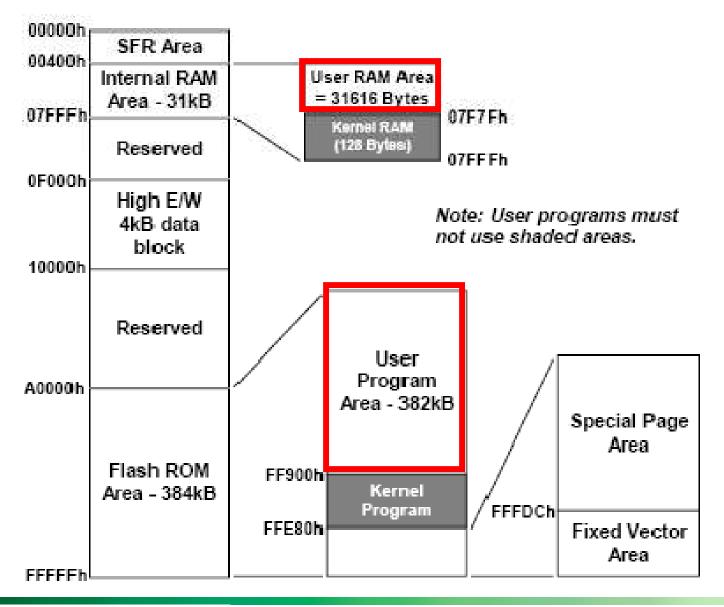

# **General Memory Map**

# Memory Map for QSK62P Plus microcontroller

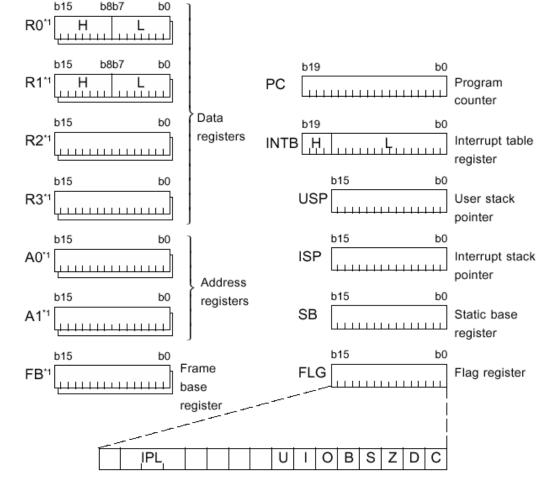

# M16C Registers

- 4 16-bit data registers R0-R3

- Can also access high and low bytes of R0 and R1: R0H, R0L

- Can also access pairs of registers as 32-bit registers: R2R0, R3R1

- 2 16-bit address registers A0 & A1

- Can also access pair of registers as 32-bit register: A1A0

\*1 These registers have two register banks.

SP: Stack Pointer – for accessing call stack

- USP: User code

- ISP: Interrupt code

- FB: Frame Base for accessing frame on call stack

- **SB:** Static Base

**INTB:** Interrupt table pointer

See Ch. 2 of Software Manual for details

Immediate – provide the 8, 16 or 20 bit value

Register Direct – provide the name of the register

- MOV.B **#-29**, R0H

- Absolute provide the address of the operand

- MOV.W R3, 213AH

- MOV.W 81A8H, R3

Α

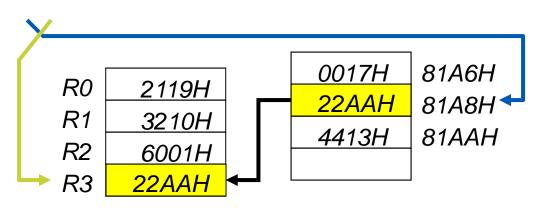

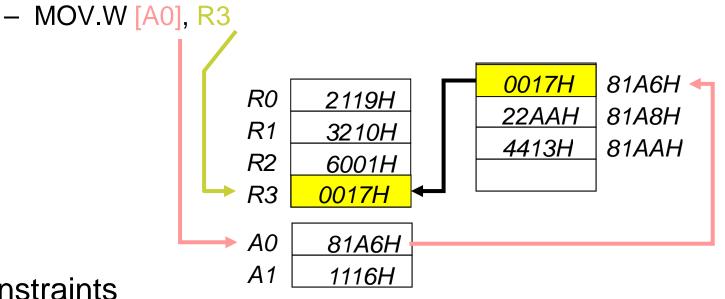

Address Register Indirect – provide the name of the address register which points to the operand

#### **Constraints**

Can use address registers A0 and A1

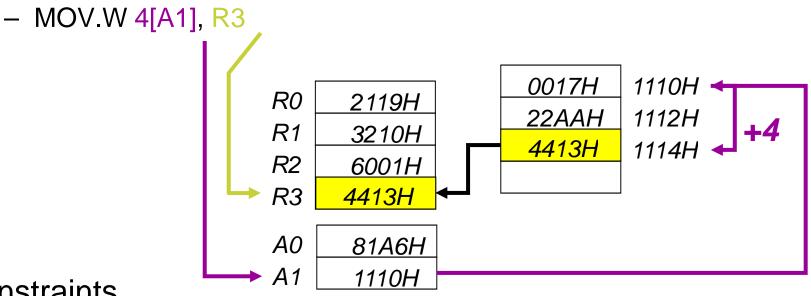

Address Register Relative – as with ARI, but also provide a displacement (offset) from the address register

Constraints

- Can use address registers A0 or A1

- Displacement can range from 0 to FFFFH

А

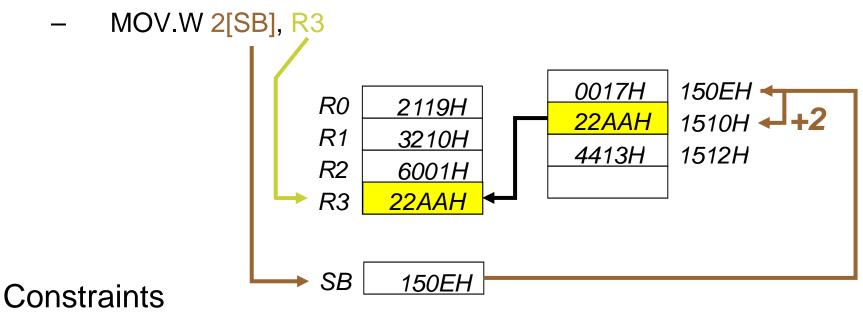

Static Base Pointer Relative – as with ARR, but use the SB as the base

- Can only use SB

- Displacement can range from 0 to FFFFH

А

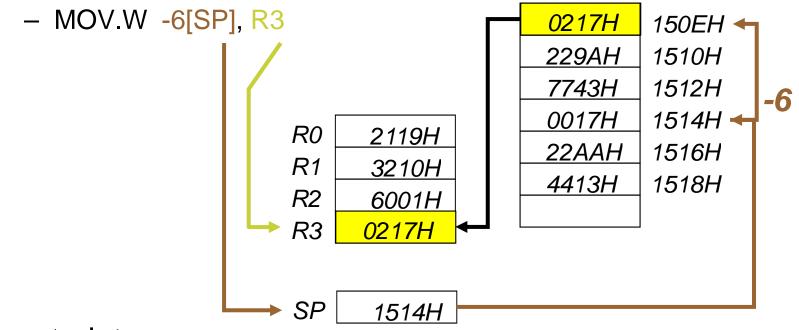

Frame Base/Stack Pointer Relative – as with ARR, but use the FB or SP register as the base

Constraints

- Can only use FB and SP

- Signed displacement can range from 80H to 7FH (-128 to +127)

Α

Data Transfer Arithmetic and Logic Control Transfer Other

#### Not load-store architecture

| <ul> <li>Transfer instructions</li> </ul>                    | MOV, MOVA                      |

|--------------------------------------------------------------|--------------------------------|

| <ul> <li>Push/pop instructions</li> </ul>                    | PUSH, PUSHM, PUSHA / POP, POPM |

| <ul> <li>Extended data area transfer instructions</li> </ul> | LDE, STE                       |

| <ul> <li>4-bit transfer instructions</li> </ul>              | MOVDir                         |

| <ul> <li>Exchange between register and register/</li> </ul>  | XCHG                           |

| memory instruction                                           |                                |

| <ul> <li>Conditional transfer instructions</li> </ul>        | STZ, STNZ, STZX                |

# **Arithmetic and Logic Instructions**

| <ul> <li>Add instructions</li> <li>Subtract instructions</li> <li>Multiply instructions</li> </ul> | ADD, ADC, ADCF<br>SUB, SBB<br>MUL, MULU |

|----------------------------------------------------------------------------------------------------|-----------------------------------------|

| <ul> <li>Divide instructions</li> </ul>                                                            | DIV, DIVU, DIVX                         |

| <ul> <li>Decimal add instructions</li> </ul>                                                       | DADD, DADC                              |

| <ul> <li>Decimal subtract instructions</li> </ul>                                                  | DSUB, DSBB                              |

| <ul> <li>Increment/decrement instructions</li> </ul>                                               | INC / DEC                               |

| <ul> <li>Sum of products instruction</li> </ul>                                                    | RMPA                                    |

| <ul> <li>Compare instruction</li> </ul>                                                            | CMP                                     |

| Others                                                                                             | ABS, NEG, EXTS                          |

| (absolute value, 2's complement, sign extension)                                                   | AND, OR, XOR, NOT                       |

| <ul> <li>Logic instructions</li> </ul>                                                             |                                         |

| Test instruction                                                                                   | TST                                     |

| <ul> <li>Shift/rotate instructions</li> </ul>                                                      | SHL, SHA / ROT, RORC, ROLC              |

# **Control Transfer**

| <ul> <li>Unconditional branch instruction</li> </ul>         |

|--------------------------------------------------------------|

| <ul> <li>Conditional branch instruction</li> </ul>           |

| <ul> <li>Indirect jump instruction</li> </ul>                |

| <ul> <li>Special page branch instruction</li> </ul>          |

| <ul> <li>Subroutine call instruction</li> </ul>              |

| <ul> <li>Indirect subroutine call instruction</li> </ul>     |

| <ul> <li>Special page subroutine call instruction</li> </ul> |

| <ul> <li>Subroutine return instruction</li> </ul>            |

| <ul> <li>Add (subtract) and conditional branch</li> </ul>    |

| instructions                                                 |

JMP JCnd JMPI JMPS JSR JSRI JSRS RTS ADJNZ, SBJNZ

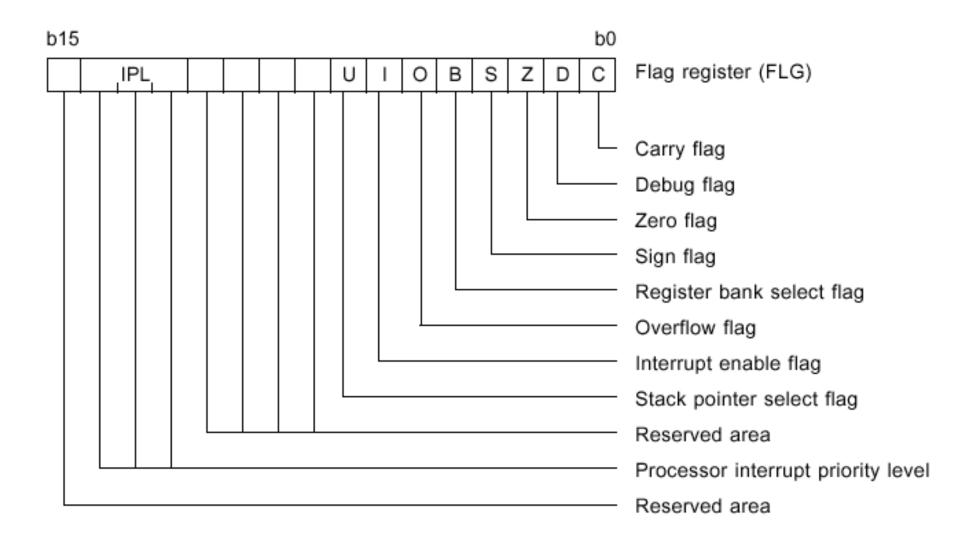

# **Flag Register and Conditions**

# **Conditional Jumps**

| Mnemonic | Description Format | Explanation                                                                                   |

|----------|--------------------|-----------------------------------------------------------------------------------------------|

| JCnd     | JCnd label         | Jumps to label if condition is true<br>or executes next instruction if<br>condition is false. |

| Cnd    | True/false determining conditions (14 conditions) |                                  |

|--------|---------------------------------------------------|----------------------------------|

| GEU/C  | C = 1                                             | Equal or greater/ Carry flag = 1 |

| GTU    | C = 1 & Z = 0                                     | Unsigned and greater             |

| EQ/Z   | Z = 1                                             | Equal/ Zero flag = 1             |

| Ν      | S = 1                                             | Negative                         |

| LE     | (Z = 1)   (S = 1 & O = 0)   (S = 0 & O = 1)       | Equal or signed and smaller      |

| 0      | O = 1                                             | Overflow flag = 1                |

| GE     | (S = 1 & O = 1)   (S = 0 & O = 0)                 | Equal or signed and greater      |

| LTU/NC | C = 0                                             | Smaller/ Carry flag = 0          |

| LEU    | C = 0   Z = 1                                     | Equal or smaller                 |

| NE/NZ  | Z = 0                                             | Not equal/ Zero flag = 0         |

| PZ     | S = 0                                             | Positive or zero                 |

| GT     | (S = 1 & O = 1 & Z = 0)   (S = 0 & O = 0 & Z = 0) | Signed and greater               |

| NO     | O = 0                                             | Overflow flag = 0                |

| LT     | (S = 1 & O = 0)   (S = 0 & O = 1)                 | Signed and smaller               |

Assembler Language Programming Manual, Sect. 2.6.1 and jump instruction definitions (p. 80) Example: CMP.W R1, R2 ; set cond. flags ; based on R2-R1 JGTU Label2 ; Jump if R1>R2

Range of jump : -127 to +128 (PC relative) for GEU/C, GTU, EQ/Z, N, LTU/NC, LEU, NE/NZ, and PZ -126 to +129 (PC relative) for LE, O, GE, GT, NO, and LT

# **Other Instructions**

| <ul> <li>Control register manipulate instructions</li> </ul> | LDC, STC, LDINTB, LDIPL, PUSHC, POPC |

|--------------------------------------------------------------|--------------------------------------|

| <ul> <li>Flag register manipulate instructions</li> </ul>    | FSET, FCLR                           |

| <ul> <li>OS support instructions</li> </ul>                  | LDCTX, STCTX                         |

| <ul> <li>High-level language support instructions</li> </ul> | ENTER, EXITD                         |

| <ul> <li>Debugger support instruction</li> </ul>             | BRK                                  |

| <ul> <li>Interrupt-related instructions</li> </ul>           | REIT, INT, INTO, UND                 |

| <ul> <li>External interrupt wait instruction</li> </ul>      | WAIT                                 |

| No-operation instruction                                     | NOP                                  |

| •                                                            | :                                    |