## **Architecture Research and IC Design for Embedded Ultra – Micro Processor**

-by Rohith Tenneti Seetha Sai

#### Introduction

#### Embedded System Design

- Simplex parallel combinational Circuit

- ✓ High Speed, small circuit area and high performance Advantage

- ✓ Complex design needs, debugging Disadvantage

- Use a general processor

- ✓ Design based on processor is fast and easy to debug Advantage

- ✓ Area, less cost performance Disadvantage

- Simplification without RAM or ROM access

- ✓ Immediate and Register addressing modes are considered no access of memory in the Instruction set architecture level

- Registers are mapped as in / out ports

- 16 bit instruction encoding, sixteen 8 bit registers

- three instruction types: double-operand instruction, single-operand instruction and branch instruction.

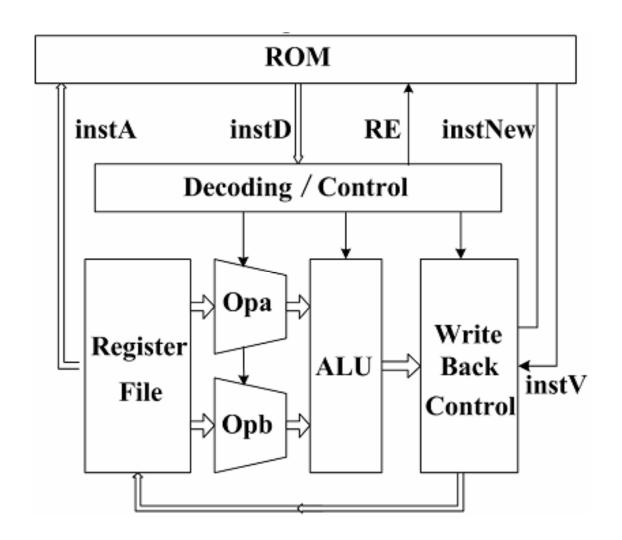

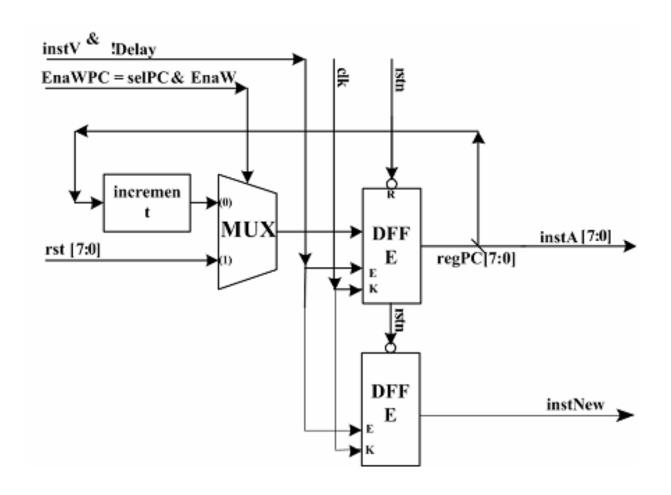

## IC Design of UMP – General Architecture

## **Instruction formats**

| Format | instD[15:0]                              |           |        |        |             |        |       |        |             |           |       |      |        |           |   |   |

|--------|------------------------------------------|-----------|--------|--------|-------------|--------|-------|--------|-------------|-----------|-------|------|--------|-----------|---|---|

|        | 15                                       | 14        | 13     | 12     | 11          | 10     | 9     | 8      | 7           | 6         | 5     | 4    | 3      | 2         | 1 | 0 |

|        | MO V/ADD/S UB/C MP/AND/O R/XO R Ra,Rb    |           |        |        |             |        |       |        |             |           |       |      |        |           |   |   |

| 1a     | inselimm                                 | infunc    |        | insela |             |        |       | inselb |             |           |       | xxxx |        |           |   |   |

|        | (0)                                      | (000-110) |        |        | (0000-1111) |        |       |        | (0000-1111) |           |       |      |        |           |   |   |

|        | MO V/ADD/S UB/C MP/AND/O R/XO R Ra,#im m |           |        |        |             |        |       |        |             |           |       |      |        |           |   |   |

| 1 b    | inselimm                                 | infunc    |        |        | insela      |        |       |        | inimm       |           |       |      |        |           |   |   |

|        | (1)                                      | (00       | 00-11  | 0)     | (0000-1111) |        |       |        | (00H-FFH)   |           |       |      |        |           |   |   |

|        | NOT/SHR/SHL Ra    GEIC/SEIC Ra,n         |           |        |        |             |        |       |        |             |           |       |      |        |           |   |   |

| 2      | inselimm                                 | infunc    |        |        | insela      |        |       |        | x           | inmon     | f     | х    | inoptn |           | n |   |

|        | (0)                                      |           | (111)  |        | (           | 0000   | -1111 | )      | ^           | (0        | 00-10 | )0)  | ^      | (000-111) |   |   |

|        | JMP/JC/J                                 | NC/J      | Z/JN   | Z #iı  | nm          |        |       |        |             |           |       |      |        |           |   |   |

| 3      | inselimm                                 | i         | infunc |        | v           | injpcf |       |        | inimm       |           |       |      |        |           |   |   |

|        | (1)                                      |           | (111)  |        | Х           | (0     | 00-10 | 0)     |             | (00H-FFH) |       |      |        |           |   |   |

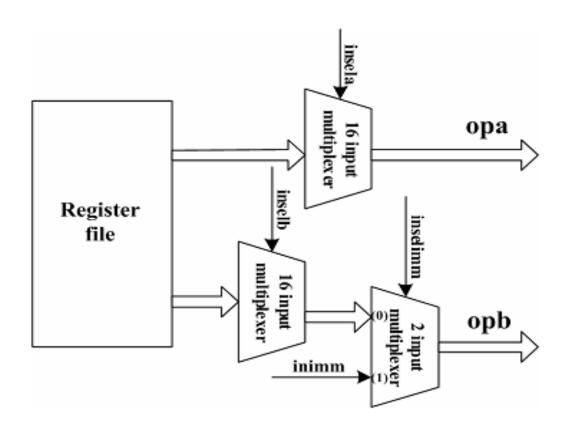

# **Operand Fetch Logic**

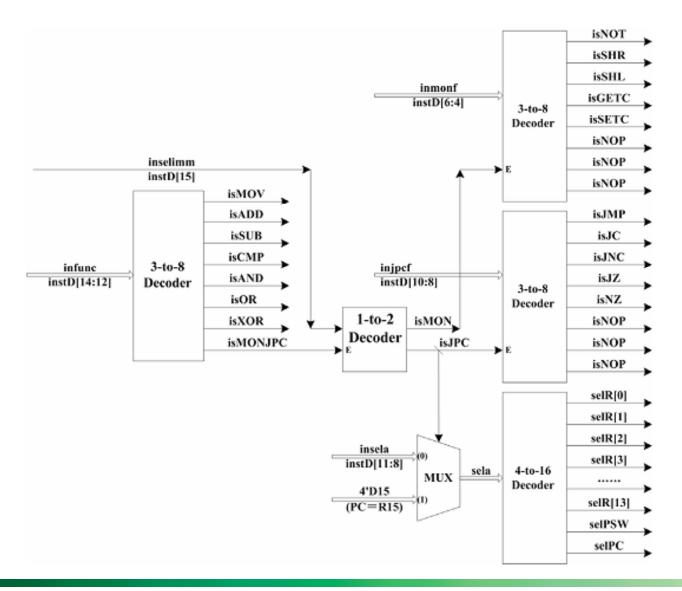

## **Instruction Decoding**

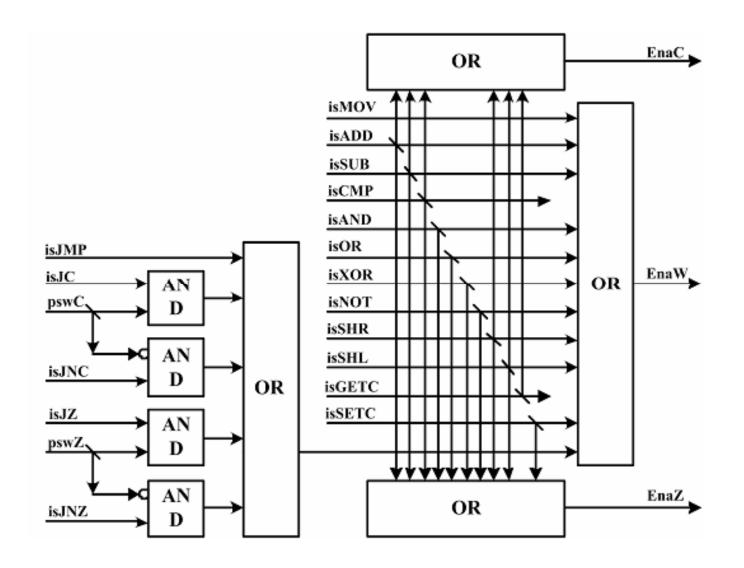

## **Enable Logic**

### Write back

### **Shoot Questions**